W42C32-05M 查看數據表(PDF) - Cypress Semiconductor

零件编号

产品描述 (功能)

比赛名单

W42C32-05M Datasheet PDF : 8 Pages

| |||

2-05M

W42C32-05M

Spread Spectrum Frequency Timing Generator

Features

• Maximized EMI suppression using Cypress’s Spread

Spectrum technology

• Generates a spread spectrum timing signal

• Reduces measured EMI by as much as 12 dB

• Integrated loop filter components

• Requires a single low-cost fundamental crystal (or

other frequency reference) for proper operation

• Special spread spectrum control functions

• Low-power CMOS design

• Power-down mode reduces current consumption and

disables the clock outputs

• Available in 16-pin SOIC package (300 mil)

Overview

The W42C32-05M modulates the output of a single PLL in

order to ‘spread’ the bandwidth of a synthesized clock and,

more importantly, decrease the peak amplitudes of its funda-

mental harmonics. Since peak amplitudes are reduced, the

radiated electromagnetic emissions of the W42C32-05M are

significantly lower than the typical narrow band signal pro-

duced by oscillators and most frequency generators. Lowering

a signal’s amplitude by increasing its bandwidth is a method of

reducing EMI called ‘spread spectrum frequency timing gen-

eration’. This patented technique not only reduces the emis-

sions of the primary clock, but also impacts every signal syn-

chronized to it.

Key Specifications

Cycle-to-Cycle Jitter .................................................... 250 ps

45/55 Duty Cycle .................................... approximately 1.4V

Selectable Frequency spread

2 ns rise/fall time 0.4V to 2.0V, 3.3V supply

2 ns rise/fall time 0.8V to 2.4V, 5.0V supply

Table 1. Frequency Spread Selection

W42C32-05M

REFOUT

FS2 FS1 FS0 (MHz)

CLKOUT

(MHz)

VDD

(V)

0

0

0 22.1148

44.2296 ±

5.0

2.5%

0

0

1 22.1148

44.2296

5.0

±1.5%

0

1

0 14.7456

29.4912 ±

5.0

2.5%

0

1

1

18.432 18.432 ± 2.5% 5.0

1

0

0

14.318

66.66 – 2%

3.3

1

0

1

Reserved

3.3

1

1

0

14.318

100 – 2%

3.3

1

1

1

Reserved

3.3

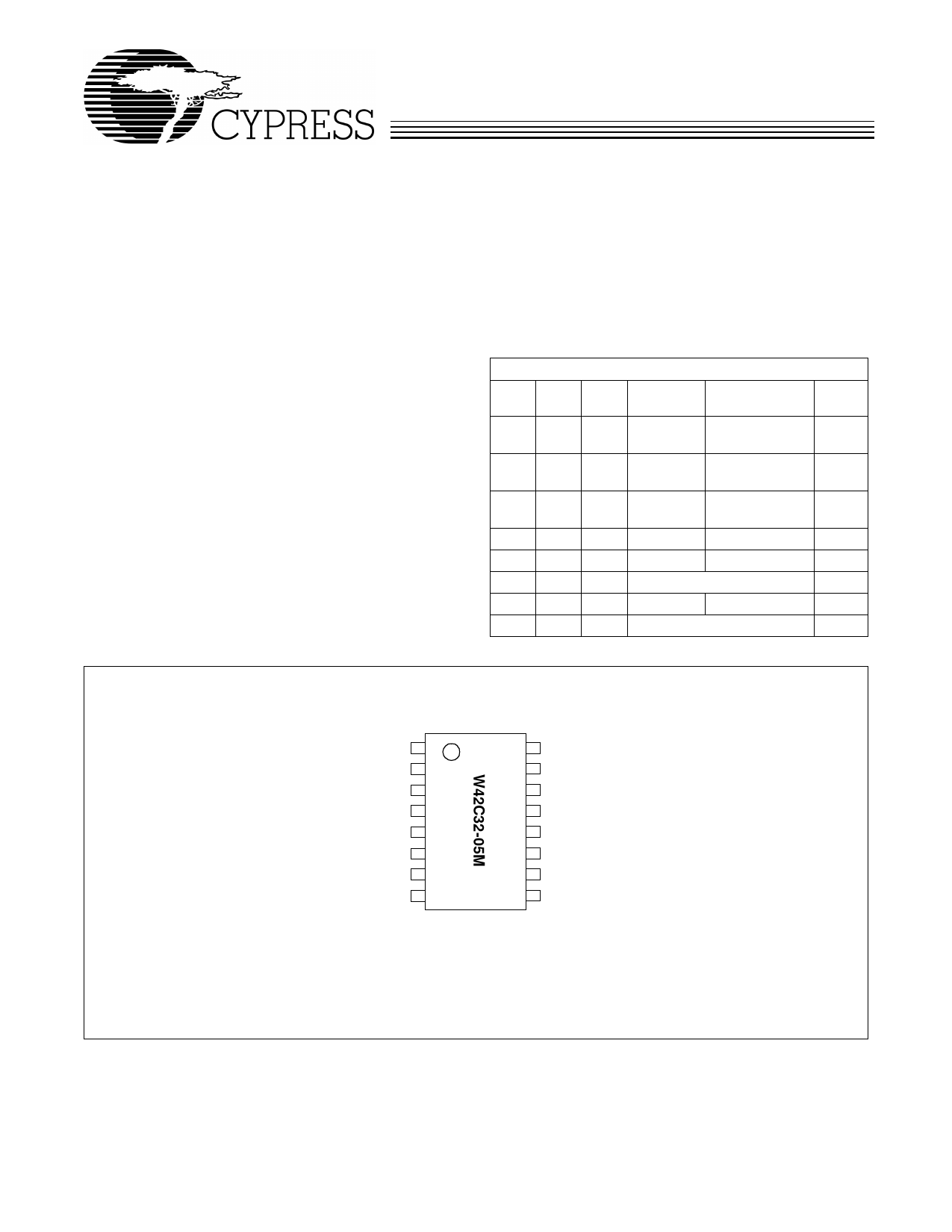

Pin Configuration

PD#

X1

X2

GND

AGND

FS0

TEST

CLKOUT

SOIC

1

16

2

15

3

14

4

13

5

12

6

11

7

10

8

9

REFOUT

FS2

FS1

SSON#

RESET

VDD

AVDD

REFEN#

Cypress Semiconductor Corporation • 3901 North First Street • San Jose • CA 95134 • 408-943-2600

January 5, 2001, rev. **