CL8452A 查看數據表(PDF) - Clear Logic

零件编号

产品描述 (功能)

比赛名单

CL8452A Datasheet PDF : 12 Pages

| |||

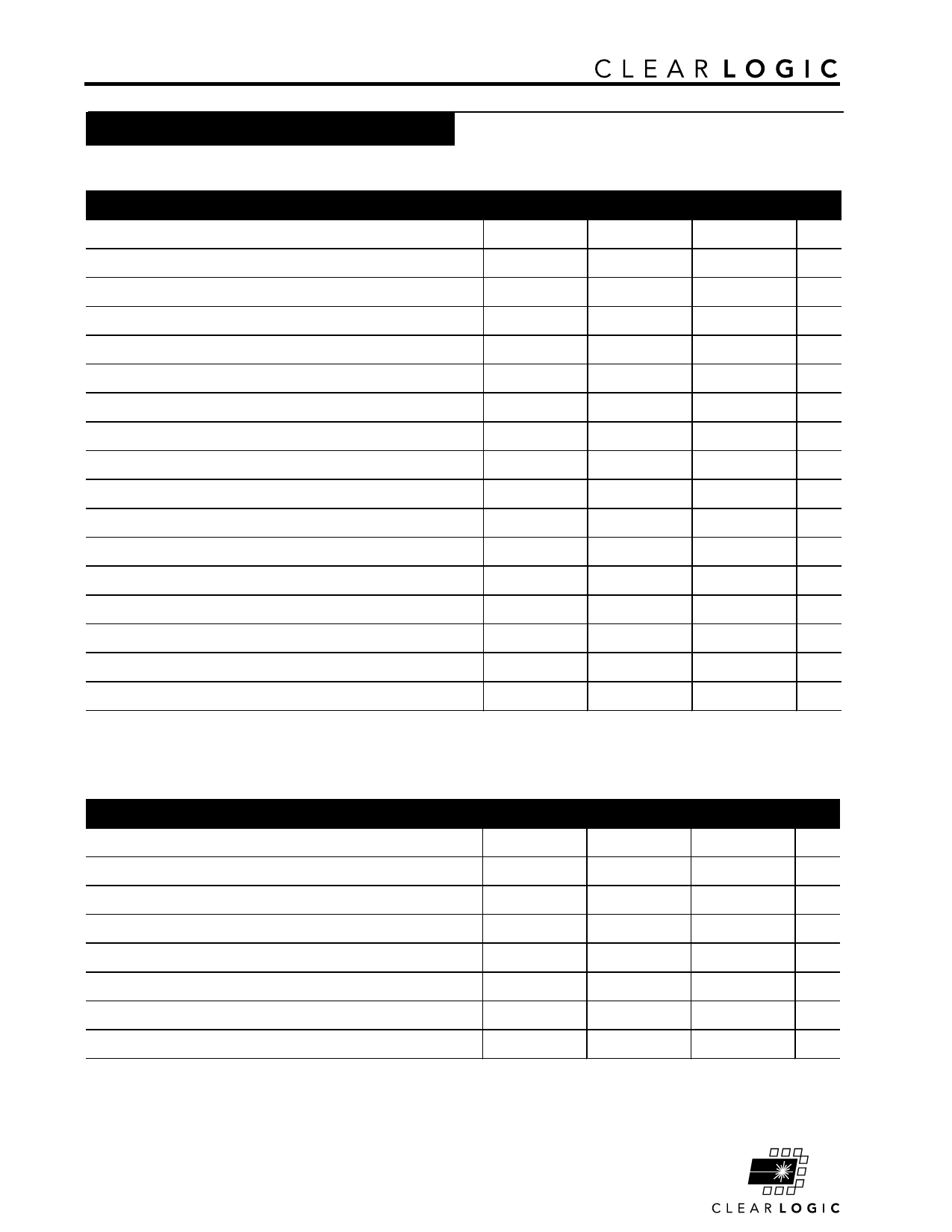

CL8452A Laser-Configured ASIC

AC Electrical Specifications cont.

Logic Element Timing Parameters[5] Speed: -2

Symbol

Parameter

Conditions Min Max

tLUT Look up table delay for data-in

2.0

tCLUT Look up table delay for carry-in

0.0

tRLUT Look up table delay for LE register feedback

0.9

tGATE Cascade gate delay

0.0

tCASC Cascade chain routing delay

0.6

tCICO Carry-in to carry-out delay

0.4

tCGEN Data-in to carry-out delay

0.4

tCGENR LE register feedback to carry-out delay

0.9

tC LE register control signal delay

1.6

tCH Clock high time

1.7

tCL Clock low time

1.7

tCO LE register clock-to-output delay

0.4

tCOMB Combinatorial delay

0.4

tSU LE register setup time before clock

0.8

tH LE register hold time after clock

0.9

tPRE LE register preset delay

0.6

tCLR LE register clear delay

0.6

Speed: -3

Min Max

2.3

0.2

1.6

0.0

0.7

0.5

0.9

1.4

1.8

1.7

1.7

0.5

0.5

1.0

1.1

0.7

0.7

Speed: -4

Min Max Unit

3.0 ns

0.1 ns

1.6 ns

0.0 ns

0.9 ns

0.6 ns

0.8 ns

1.5 ns

2.4 ns

2.7

ns

2.7

ns

0.6 ns

0.6 ns

1.1

ns

1.4

ns

0.8 ns

0.8 ns

8K tbl 08B

Interconnect Timing Parameters[5]

Speed: -2

Symbol

Parameter

Conditions Min Max

tLABCASC Cascade delay between LEs in different LABs

0.3

tLABCARRY Carry delay between LEs in different LABs

0.3

tLOCAL LAB local interconnect delay

0.5

tROW Row interconnect routing delay

5.0

tCOL Column interconnect routing delay

3.0

tDIN_C Dedicated input to LE control delay

5.0

tDIN_D Dedicated input to LE data delay

7.0

tDIN_IO Dedicated input to IOE control delay

5.0

Speed: -3

Min Max

0.4

0.4

0.5

5.0

3.0

5.0

7.0

5.0

Speed: -4

Min Max Unit

0.4 ns

0.4 ns

0.7 ns

5.0 ns

3.0 ns

5.5 ns

7.5 ns

5.5 ns

8K tbl 09B

Page 10