MSM7580 查看數據表(PDF) - Oki Electric Industry

零件编号

产品描述 (功能)

比赛名单

MSM7580 Datasheet PDF : 18 Pages

| |||

¡ Semiconductor

MSM7580

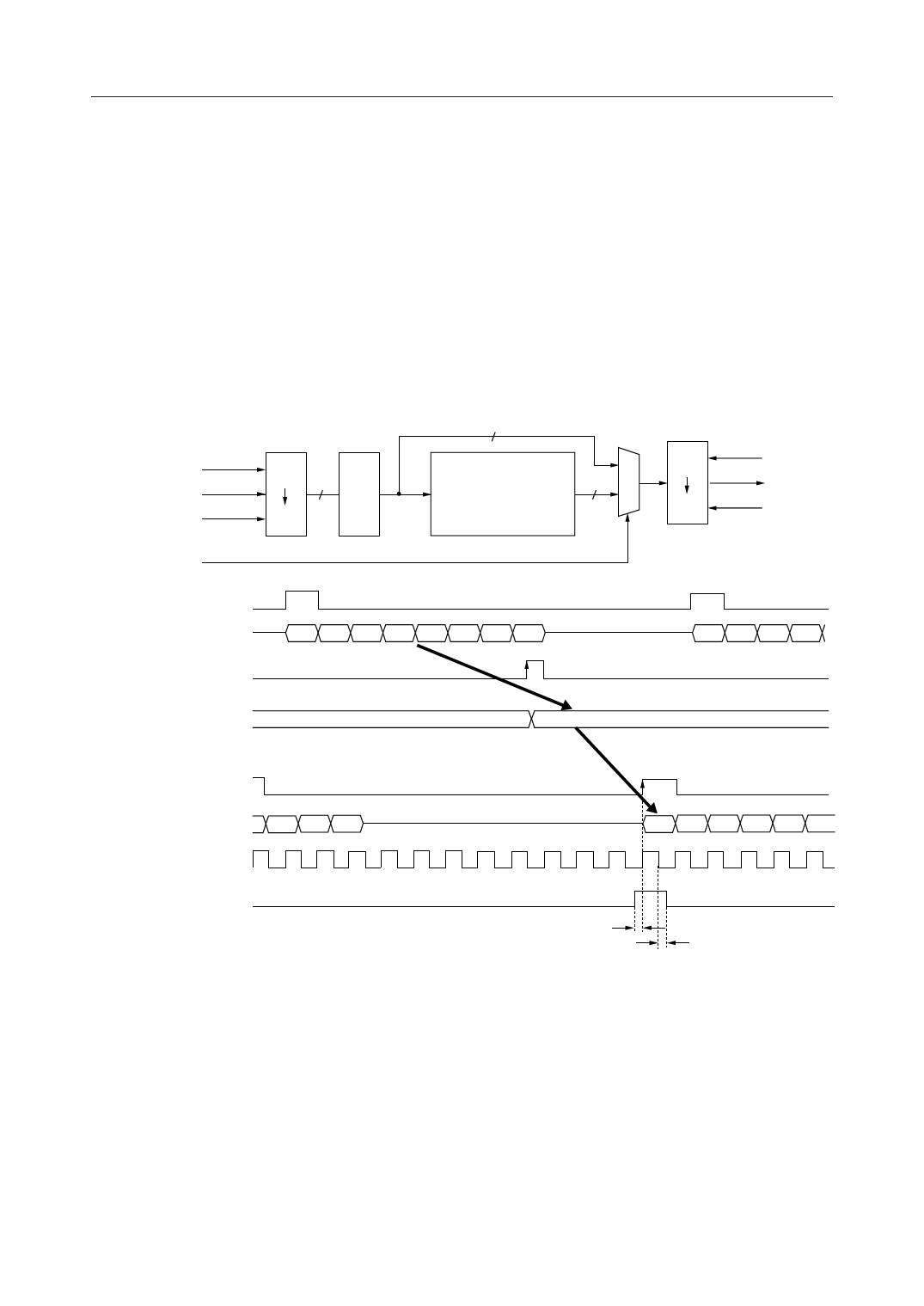

THR Processing Timing

Timing Block Diagrams, when CODER and DECODER output data, are shown in the following

figures.

The parallel to serial conversion of the output unit employs a load format and the load point is

at the rising edge of a synchronous signal.

Therefore, input THR signal with respect to SYNCA for CODER with timing of satisfying ts and

th conditions shown in the figure.

For DECODER, THR signal should be input even when through-data is input.

The input timing should satisfy the conditions shown in the following figures.

CODER

SYNCP

SIP

BCLKP

THR

Serial 8

Parallel

Latch

Latch timing=A

PCM side SYNC (SYNCP)

PCM Input (SIP)

MSB

Internal Latch timing (A)

Through-data

8b

ADPCM

CODER

S

E

L

4b

Parallel

Serial

LSB

SYNCA

SOA

BCLKA

Internal Input Data

Through-data

ADPCM side SYNC (SYNCA)

Through-data Output (SOA)

MSB

BCLKA

THR

ts

th

ts=100ns or more

th=100ns or more

Note: That data-ship may occur when the rising edge (data load point) of SYNCA and input of

the internal latch timing overlap each other.

11/17