HS-80C86RH 查看數據表(PDF) - Intersil

零件编号

产品描述 (功能)

比赛名单

HS-80C86RH Datasheet PDF : 29 Pages

| |||

HS-80C86RH

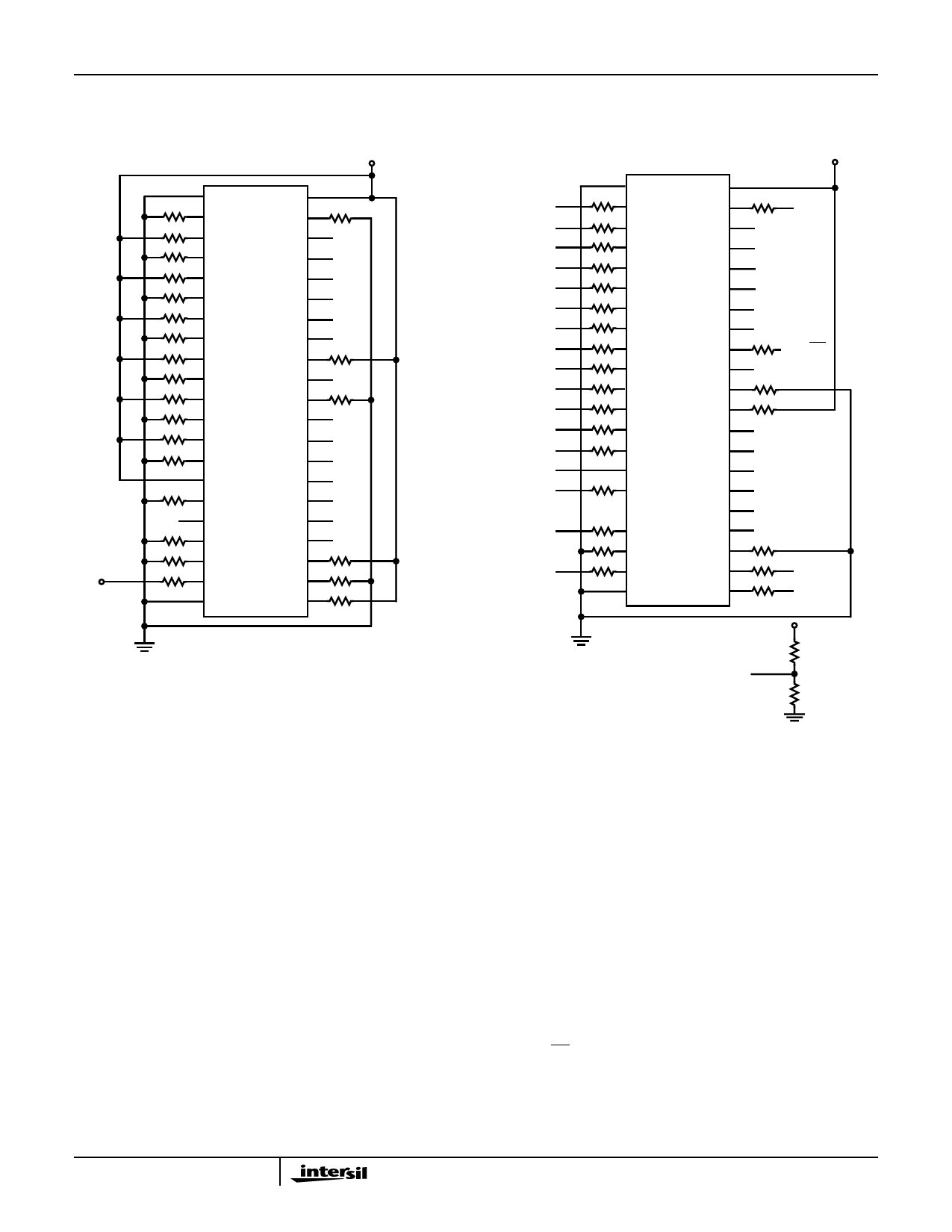

Burn-In Circuits (Continued)

HS-80C86RH 42 LEAD FLATPACK

VDD

1

42

F15

2

41

F14

3

40

F13

4

39

F12

5

38

F11

6

37

F10

7

36

F9

8

35

F8

9

34

F7

10

33

F6

11

32

F5

12

31

F4

13

30

F3

14

29

F2

15

28

F1

16

27

17

26

NMI

18

25

19

24

CLK

F0

20

23

21

22

HS-80C86RH 42 LEAD FLATPACK

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

OPEN 17

18

19

20

21

VDD

42

41

F16

40

OPEN

39

LOAD

38

LOAD

37

LOAD

36

LOAD

35

LOAD

34

MN/MX

33

LOAD

32

31

30

LOAD

29

LOAD

28

LOAD

27

LOAD

26

LOAD

25

LOAD

24

23

READY

22

RESET

LOAD

VDD

2.7kΩ

2.7kΩ

STATIC

NOTES:

28. VDD = +6.5V ±10%.

29. TA = 125oC Minimum.

30. Part is Static Sensitive.

31. Voltages Must Be Ramped.

32. Package: 42 Lead Flatpack.

33. Resistors:

10kΩ ±10%

(Pins 18, 19, 22-24, 32, 34)

2.7kΩ ±5% (Pins 2-16, 41)

1.0kΩ ±5% 1/10W Min (Pin 20)

Minimum of 5 CLK Pulses

After Initial Pulses, CLK is Left High

Pulses are 50% Duty Cycle Square Wave

DYNAMIC

NOTES:

34. VDD = 6.5V ±5% (Burn-In).

35. VDD = 6.0V ±5% (Life Test).

36. TA = 125oC.

37. Package: 42 Lead Flatpack.

38. Part is Static Sensitive.

39. Voltage Must Be Ramped.

40. Resistors:

10kΩ (Pins 17, 18, 19, 22, 23, 24, 34)

3.3kΩ (Pins 2-16, 20, 31, 32, 41)

2.7kΩ Loads As Indicated

All Resistors Are At Least 1/8W, ±10%

F0 = 100kHz, F1 = F0/2, F2 = F1/2 . . .

RESET, NMI low after initialization.

READY pulsed low every 320µs

MN/MX changes state every 5.24s

10