HS-80C86RH 查看數據表(PDF) - Intersil

零件编号

产品描述 (功能)

比赛名单

HS-80C86RH Datasheet PDF : 29 Pages

| |||

HS-80C86RH

Pin Descriptions (Continued)

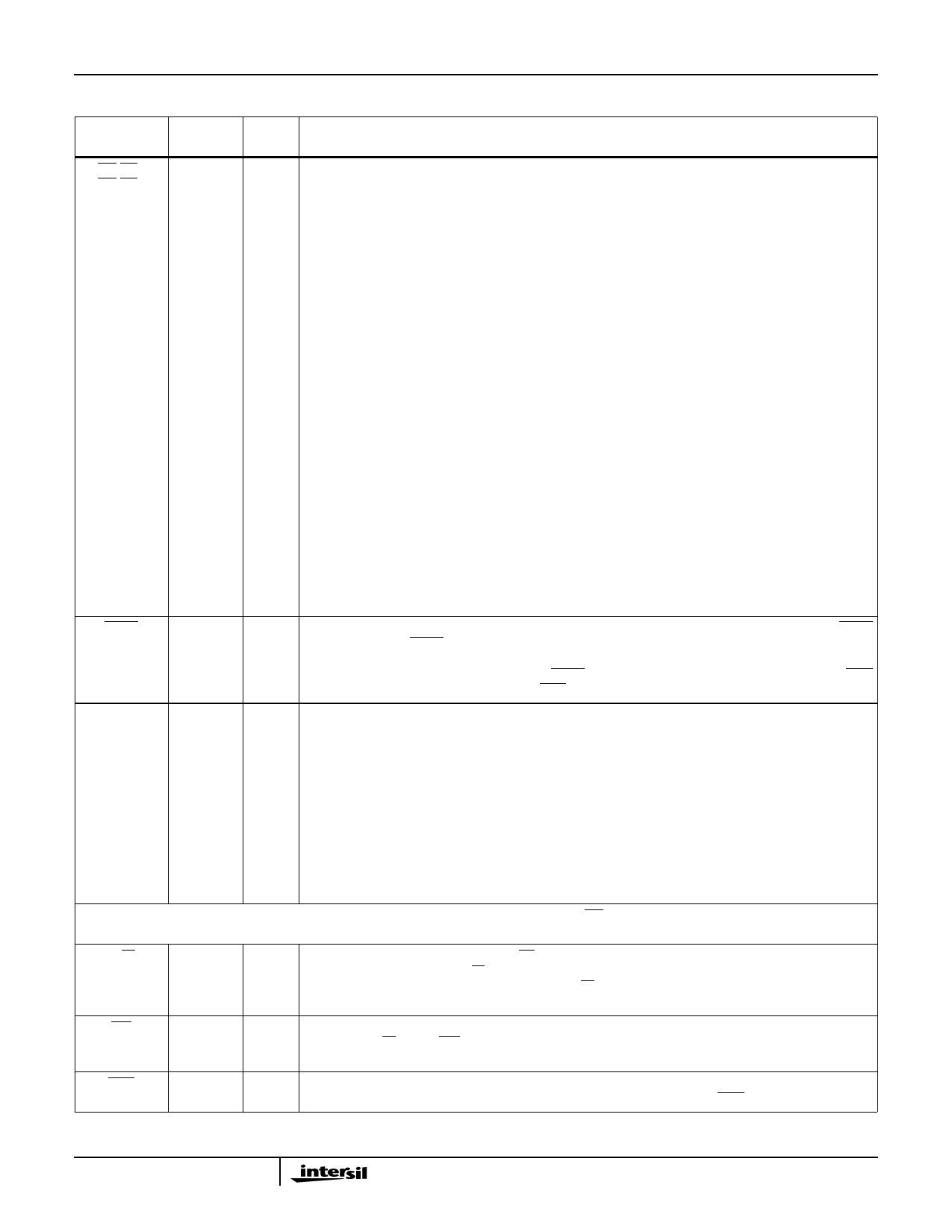

SYMBOL

PIN

NUMBER TYPE

DESCRIPTION

RQ/GT0

RQ/GT1

31, 30

I/O REQUEST/GRANT: pins are used by other local bus masters to force the processor to release the local

bus at the end of the processor’s current bus cycle. Each pin is bidirectional with RQ/GT0 having higher

priority than RQ/GT1. RQ/GT has an internal pull-up bus hold device so it may be left unconnected. The

request/grant sequence is as follows (see RQ/GT Sequence Timing.)

1. A pulse of 1 CLK wide from another local bus master indicates a local bus request (“hold”) to the

HS-80C86RH (pulse 1).

2. During a T4 or T1 clock cycle, a pulse 1 CLK wide from the HS-80C86RH to the requesting master

(pulse 2) indicates that the HS-80C86RH has allowed the local bus to float and that it will enter the

“grant sequence” state at the next CLK. The CPU’s bus interface unit is disconnected logically from

the local bus during “grant sequence”.

3. A pulse 1 CLK wide from the requesting master indicates to the HS-80C86RH (pulse 3) that the “hold”

request is about to end and that the HS-80C86RH can reclaim the local bus at the next CLK. The

CPU then enters T4 (or T1 if no bus cycles pending).

Each Master-Master exchange of the local bus is a sequence of 3 pulses. There must be one idle

CLK cycle after each bus exchange. Pulses are active low.

If the request is made while the CPU is performing a memory cycle, it will release the local bus during

T4 of the cycle when all the following conditions are met:

1. Request occurs on or before T2.

2. Current cycle is not the low byte of a word (on an odd address).

3. Current cycle is not the first acknowledge of an interrupt acknowledge sequence.

4. A locked instruction is not currently executing.

If the local bus is idle when the request is made the two possible events will follow:

1. Local bus will be released during the next cycle.

2. A memory cycle will start within 3 CLKs. Now the four rules for a currently active memory cycle

apply with condition number 1 already satisfied.

LOCK

29

O LOCK: output indicates that other system bus masters are not to gain control of the system bus while LOCK

is active LOW. The LOCK signal is activated by the “LOCK” prefix instruction and remains active until the

completion of the next instruction. This signal is active LOW, and is held at a HIGH impedance logic one

state during “grant sequence”. In MAX mode, LOCK is automatically generated during T2 of the first INTA

cycle and removed during T2 of the second INTA cycle.

QS1, QS0

24, 25

O QUEUE STATUS: The queue status is valid during the CLK cycle after which the queue operation is

performed.

QS1 and QS2 provide status to allow external tracking of the internal HS-80C86RH instruction queue.

Note that QS1, QS0 never become high impedance.

QS1

QS0

0

0

No Operation

0

1

First Byte of Opcode from Queue

1

0

Empty the Queue

1

1

Subsequent Byte from Queue

The following pin function descriptions are for the HS-80C86RH in minimum mode (i.e., MN/MX = VDD). Only the pin functions which are unique

to minimum mode are described; all other pin functions are as described below.

M/IO

28

O STATUS LINE: logically equivalent to S2 in the maximum mode. It is used to distinguish a memory

access from an I/O access. M/IO becomes valid in the T4 preceding a bus cycle and remains valid until

the final T4 of the cycle (M = HIGH, IO = LOW). M/IO is held to a high impedance logic zero during local

bus “hold acknowledge”.

WR

29

O WRITE: indicates that the processor is performing a write memory or write I/O cycle, depending on the

state of the M/IO signal. WR is active for T2, T3 and TW of any write cycle. It is active LOW, and is held

to high impedance logic one during local bus “hold acknowledge”.

INTA

24

O INTERRUPT ACKNOWLEDGE: is used as a read strobe for interrupt acknowledge cycles. It is active

LOW during T2, T3 and TW of each interrupt acknowledge cycle. Note that INTA is never floated.

6