5962R9582001QJC 查看數據表(PDF) - Intersil

零件编号

产品描述 (功能)

比赛名单

5962R9582001QJC Datasheet PDF : 18 Pages

| |||

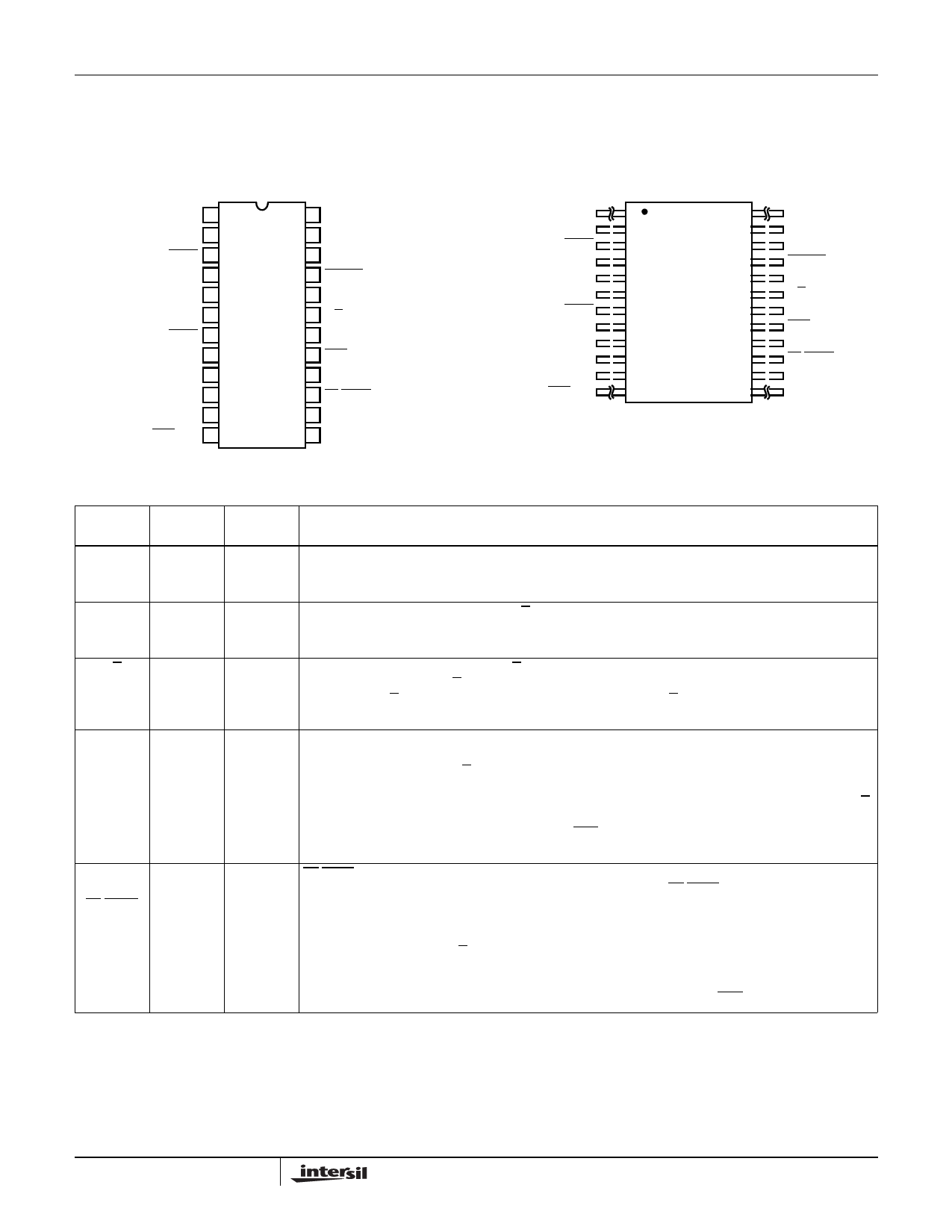

Pinouts

24 LEAD CERAMIC DUAL-IN-LINE

METAL SEAL PACKAGE (SBDIP)

MIL-STD-1835 CDIP2-T24

TOP VIEW

CSYNC 1

PCLK 2

AEN1 3

RDY1 4

READY 5

RDY2 6

AEN2 7

CLK 8

GND 9

CLK50 10

START 11

SLO/FST 12

24 VDD

23 X1

22 X2

21 ASYNC

20 EFI

19 F/C

18 OSC

17 RES

16 RESET

15 S2/STOP

14 S1

13 S0

HS-82C85RH

24 LEAD CERAMIC METAL SEAL

FLATPACK PACKAGE (FLATPACK)

MIL-STD-1835 CDFP4-F24

TOP VIEW

CSYNC

1

PCLK

2

AEN1

3

RDY1

4

READY

5

RDY2

6

AEN2

7

CLK

8

GND

9

CLK50

10

START

11

SLO/FST

12

24

VDD

23

X1

22

X2

21

ASYNC

20

EFI

19

F/C

18

OSC

17

RES

16

RESET

15

S2/STOP

14

S1

13

S0

Pin Descriptions

PIN

PIN

NUMBER

X1

23

X2

22

EFI

20

F/C

19

START

11

S0

13

S1

14

S2/STOP

15

TYPE

I

O

I

I

I

I

I

I

DESCRIPTION

CRYSTAL CONNECTIONS: X1 and X2 are the crystal oscillator connections. The crystal frequency must

be three times the maximum desired processor clock frequency. X1 is the oscillator circuit input and X2

is the output of the oscillator circuit.

EXTERNAL FREQUENCY IN: When F/C is HIGH, CLK is generated from the EFI input signal. This input

signal should be a square wave with a frequency of three times the maximum desired CLK output

frequency.

FREQUENCY/CRYSTAL SELECT: F/C selects either the crystal oscillator or the EFI input as the main

frequency source. When F/C is LOW, the HS-82C85RH clocks are derived from the crystal oscillator

circuit. When F/C is HIGH, CLK is generated from the EFI input. F/C cannot be dynamically switched

during normal operation.

A low-to-high transition on START will restart the CLK, CLK50 and PCLK outputs after the appropriate

restart sequence is completed.

When in the crystal mode (F/C LOW) with the oscillator stopped, the oscillator will be restarted when a

Start command is received. The CLK, CLK50 and PCLK outputs will start after the oscillator input signal

(X1) reaches the Schmitt trigger input threshold and an 8K internal counter reaches terminal count. If F/C

is HIGH (EFI mode), CLK, CLK50 and PCLK will restart within 3 EFI cycles after START is recognized.

The HS-82C85RH will restart in the same mode (SLO/FST) in which it stopped. A high level on START

disables the STOP mode.

S2/STOP, S1, S0 are used to stop the HS-82C85RH clock outputs (CLK, CLK50, PCLK) and are sampled

by the rising edge of CLK. CLK, CLK50 and PCLK are stopped by S2/STOP, S1, S0 being in the LHH

state on the low-to-high transition of CLK. This LHH state must follow a passive HHH state occurring on

the previous low-to-high CLK transition. CLK and CLK50 stop in the high state. PCLK stops in it’s current

state (high or low).

When in the crystal mode (F/C) low and a STOP command is issued, the HS-82C85RH oscillator will stop

along with the CLK, CLK50 and PCLK outputs. When in the EFI mode, only the CLK, CLK50 and PCLK

outputs will be halted. The oscillator circuit if operational, will continue to run. The oscillator and/or clock

is restarted by the START input signal going true (HIGH) or the reset input (RES) going low.

2

FN3044.3

April 20, 2007