5962R9582001QJC 查看數據表(PDF) - Intersil

零件编号

产品描述 (功能)

比赛名单

5962R9582001QJC Datasheet PDF : 18 Pages

| |||

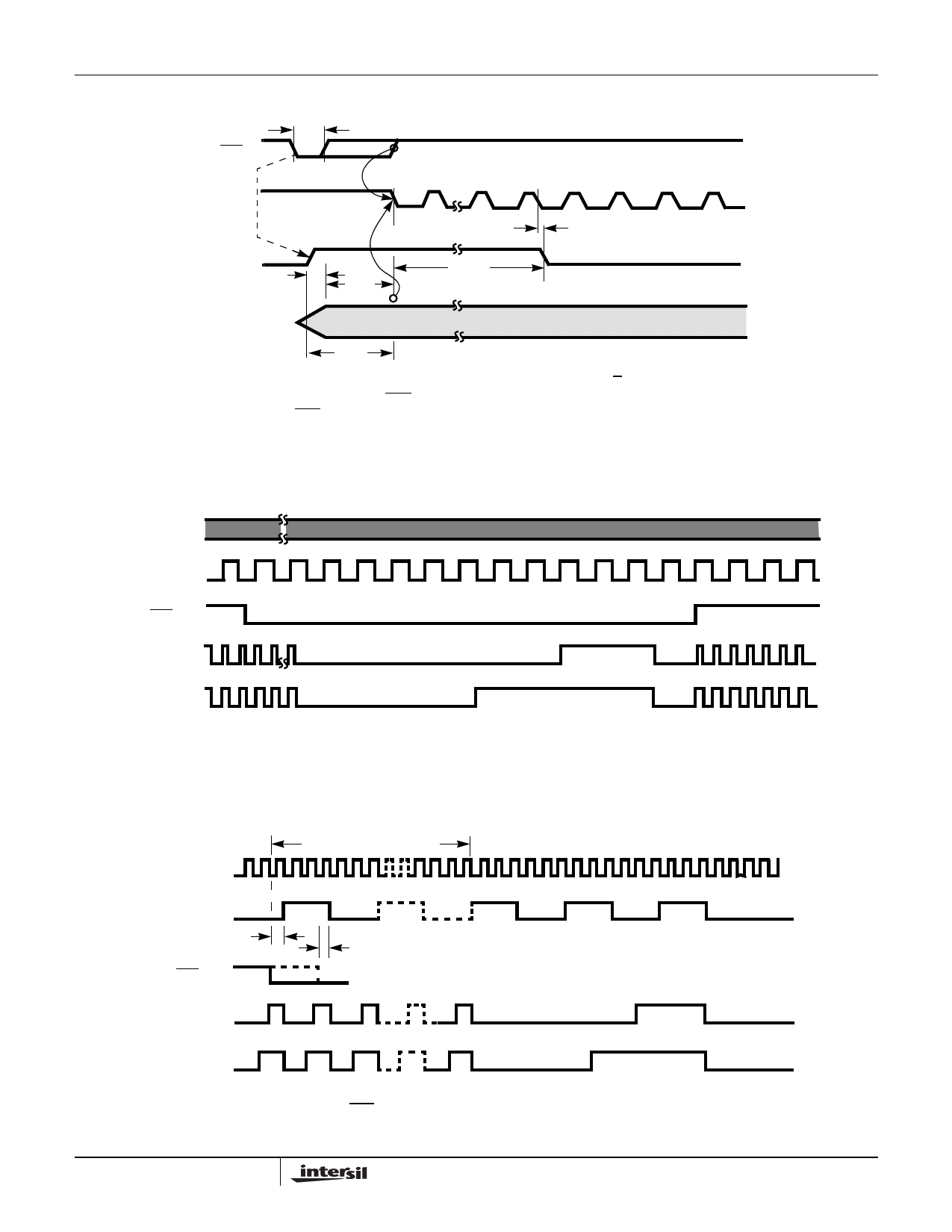

Waveforms (Continued)

RES

HS-82C85RH

tSHSL

CLK

RESET

OSC

STARTUP

TIME

OSC

8192

CYCLES

tCLIL

tRST

tOST

FIGURE 8. RESET TIMING OSCILLATOR STOPPED (F/C LOW)

NOTE: CLK, CLK50, PCLK remain in the high state until RES goes high and 8192 valid oscillator cycles have been registered by the HS-82C85RH

internal counter tOST time period). After RES goes high and CLK, CLK50, PCLK become active, the RESET output will remain high for a minimum

of 16 CLK cycles (tRST).

EFI OR OSC

PCLK

SLO/FST

CLK

CLK50

FIGURE 9. SLO/FST TIMING OVERVIEW

EFI OR OSC

PCLK

tSFPC

(NOTE)

SLO/FST

CLK

195 EFI OR OSC CYCLES

tSFPC (NOTE)

CLK50

FIGURE 10. FAST TO SLOW CLOCK MODE TRANSITION

NOTE: If tSFPC is not met on one edge of PCLK, SLO/FST will be recognized on the next edge of PCLK.

8

FN3044.3

April 20, 2007