5962F9563501QYC 查看數據表(PDF) - Intersil

零件编号

产品描述 (功能)

比赛名单

5962F9563501QYC Datasheet PDF : 36 Pages

| |||

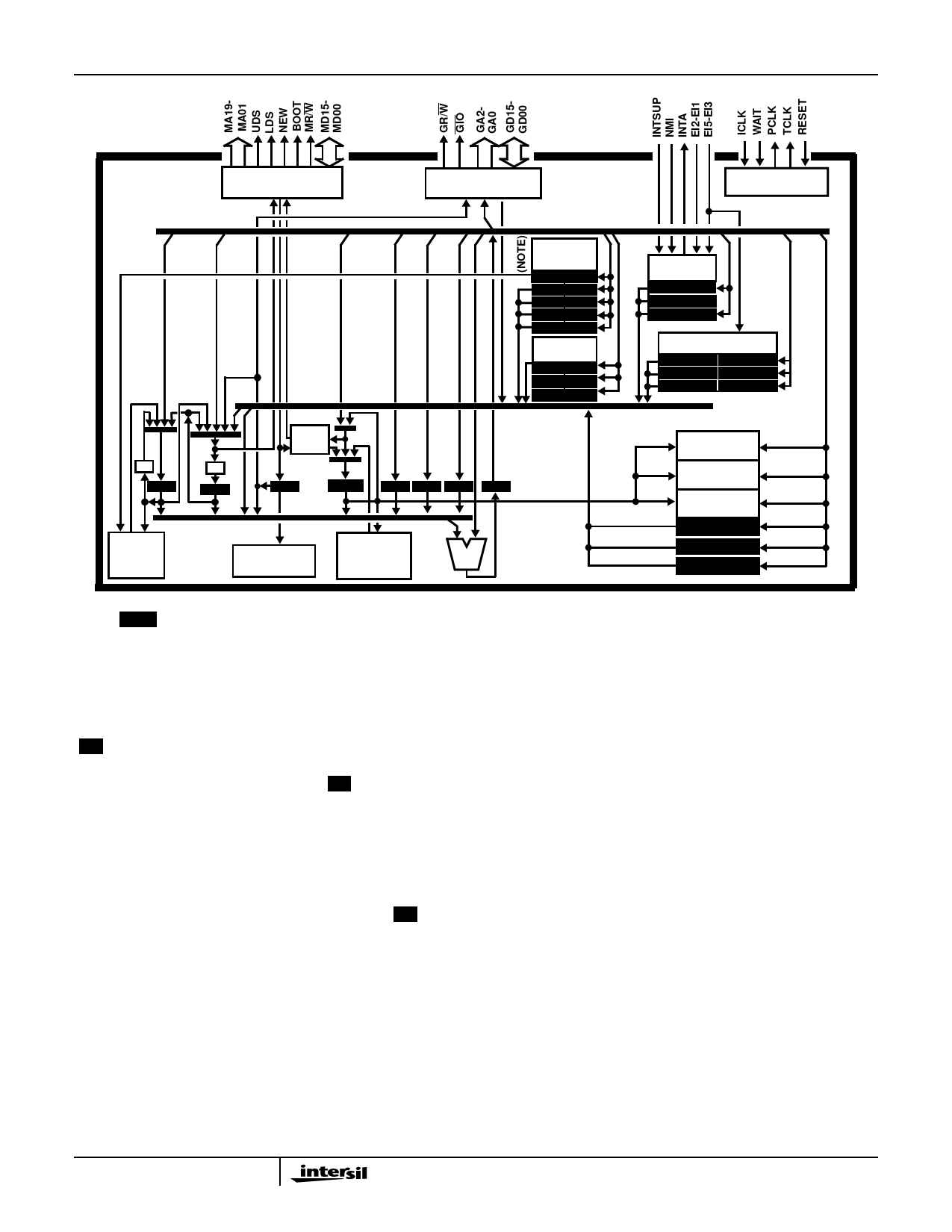

OFF-CHIP

USER

INTERFACES

HS-RTX2010RH

MEMORY BUS

INTERFACE

HS-RTX2010RH

ASIC BUS

INTERFACE

CLOCK AND

RESET CONTROL

-1

+1

I

PC

BYTE

SWAP

MEMORY

PAGE

CONTROL

IPR

DPR

UPR

CPR

UBR

STACK

CONTROL

SPR

SVR

SUR

IR

NEXT

CR MD SR TOP

256 x 21

RETURN

STACK

MEMORY

INSTRUCTION

DECODER

256 x 16

PARAMETER

STACK

MEMORY

YT

ALU

INTERRUPT

CONTROL

IMR

IVR

IBC

TIMER/COUNTERS

TC0

TP0

TC1

TP1

TC2

TP2

BARREL

SHIFTER

LEADING ZERO

DETECTOR

16 x 16

MAC

MXR

MHR

MLR

NOTE: IPR contains the 5 most significant bits (20-16) of the top element of the Return Stack.

FIGURE 9. HS-RTX2010RH FUNCTIONAL BLOCK DIAGRAM

HS-RTX2010RH Operation

Control of all data paths and the Program Counter Register,

( PC ), is provided by the Instruction Decoder. This hardware

determines what function is to be performed by looking at

the contents of the Instruction Register, ( IR ), and

subsequently determines the sequence of operations

through data path control.

Instructions which do not perform memory accesses execute

in a single clock cycle while the next instruction is being

fetched.

As shown in Figure 10, the instruction is latched into IR at

the beginning of a clock cycle. The instruction is then decoded

by the processor. All necessary internal operations are

performed simultaneously with fetching the next instruction.

Instructions which access memory require two clock cycles

to be executed. During the first cycle of a memory access

instruction, the instruction is decoded, the address of the

memory location to be accessed is placed on the Memory

Address Bus (MA19-MA01), and the memory data

(MD15-MD00), is read or written. During the second cycle,

ALU operations are performed, the address of the next

instruction to be executed is placed on the Memory Address

Bus, and the next instruction is fetched, as indicated in the

bottom half of Figure 10.

10