CDB6403 查看數據表(PDF) - Cirrus Logic

零件编号

产品描述 (功能)

比赛名单

CDB6403 Datasheet PDF : 54 Pages

| |||

CS6403

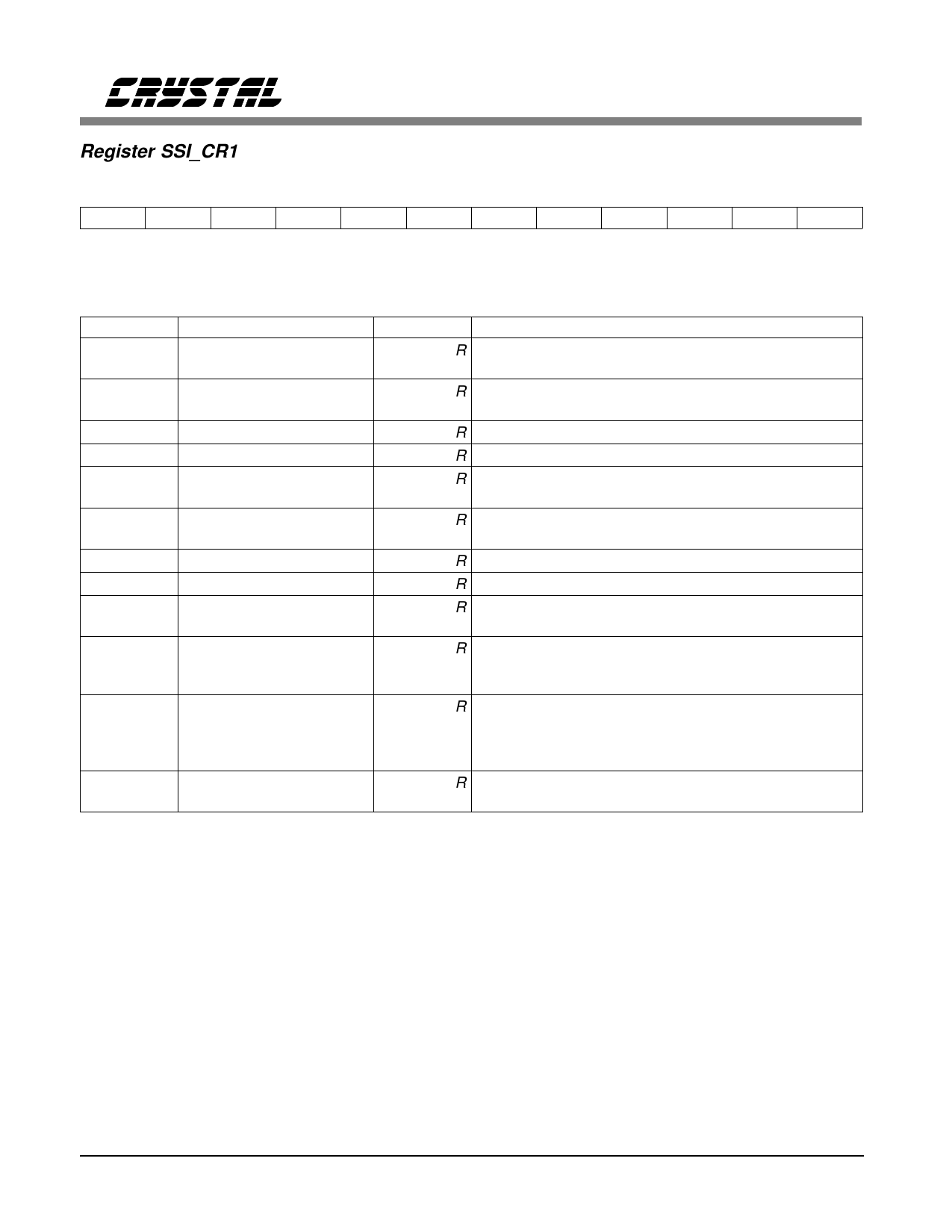

Register SSI_CR1

B11 B10

B9

CB AGCD res

0

0

0

B8

B7

B6

B5

res CAL GADCI res

0

0

0

0

B4

B3

B2

B1

B0

res NCC HDD SD ACC

0

0

0

0

0

This register is read/written by the CPU every sample time. This register is cleared at Reset by the SSI.

BIT

CB

AGCD

res

res

CAL

GADCI

res

res

NCC

HDD

NAME

Codec Bypass

AGC Disable

Reserved for test

Reserved for test

Codec Analog Loopback

Ground ADC Input

Reserved for test

Reserved for test

NEC Coefficient Clear

Half-Duplex Disable

SD

Suppression Disable

ACC

AEC Coefficient Clear

"R" indicates value after Reset

VALUE

0R

1

0R

1

0R

0R

0R

1

0R

1

0R

0R

0R

1

0R

1

0R

1

0R

1

FUNCTION

Normal operation.

Codec is bypassed by the CPU to facilitate test.

Normal operation.

AGC is disabled. Will affect volume control.

Must be 0.

Must be 0.

Normal operation.

Connect ADC to DAC internally.

Normal operation.

ADC input is grounded to facilitate test.

Must be 0.

Must be 0.

Normal operation.

The network canceller coefficients are cleared.

Normal operation.

Half-duplex mode, which is normally used during

convergence, is disabled.

Normal operation.

Supplementary suppression in the transmit path,

which normally operates in conjunction with the

echo cancellers, is disabled.

Normal operation.

The acoustic canceller coefficients are cleared.

DS192PP6

21