IDT71321 查看數據表(PDF) - Integrated Device Technology

零件编号

产品描述 (功能)

比赛名单

IDT71321 Datasheet PDF : 13 Pages

| |||

IDT71321SA/LA AND IDT71421SA/LA

HIGH-SPEED 2K x 8 DUAL-PORT STATIC RAM WITH INTERRUPTS

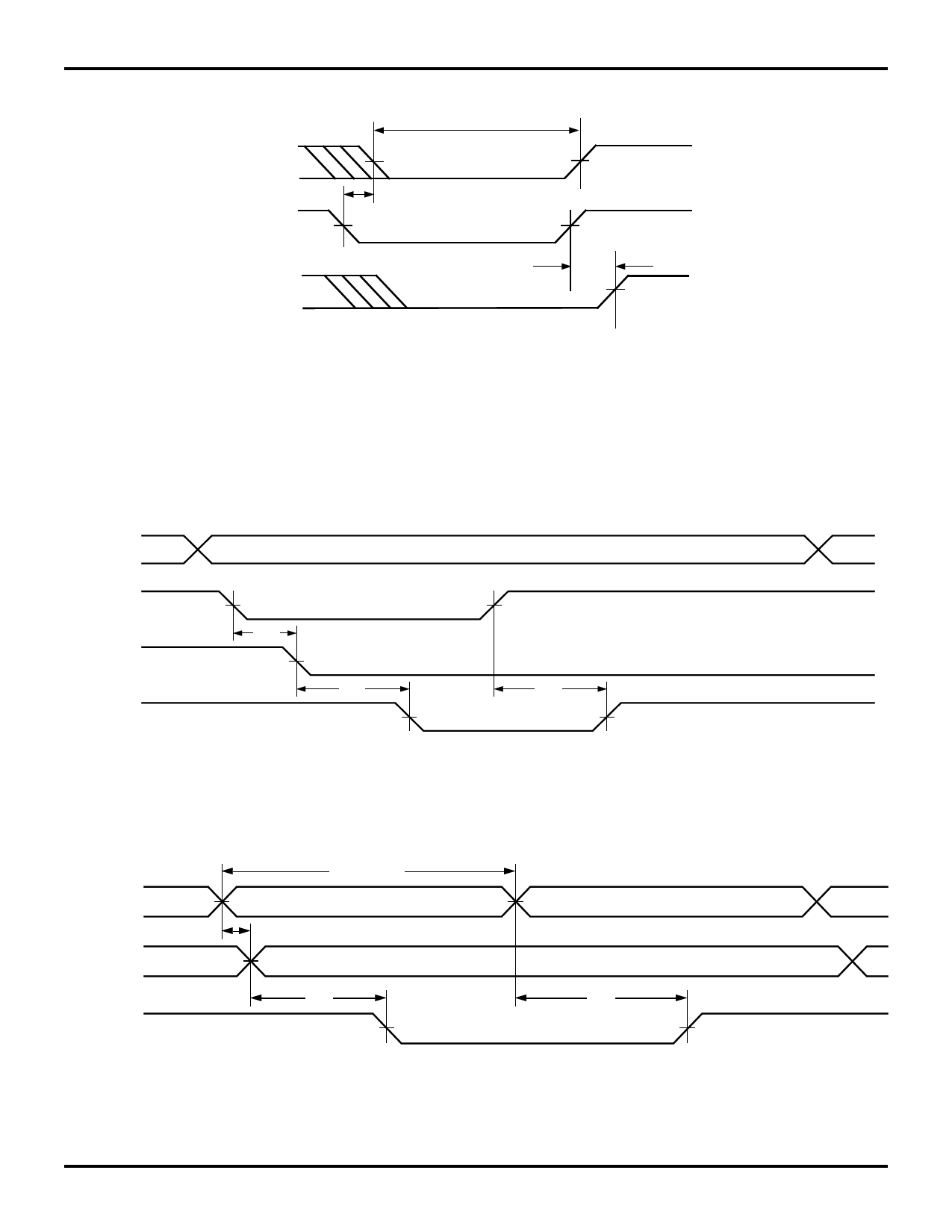

TIMING WAVEFORM OF WRITE WITH BUSY(3)

COMMERCIAL TEMPERATURE RANGE

W R/ L

BUSYR

W R/ R

tWP

tWB

(2)

(1)

tWH

2691 drw 11

NOTES:

1. tWH must be met for both BUSY Input (IDT71421, slave) or Output (IDT71321, master).

2. BUSY is asserted on port 'B' blocking R/W'B', until BUSY'B' goes High.

3. All timing is the same for the left and right ports. Port 'A' may be either the left or right port. Port 'B' is opposite from port 'A'.

TIMING WAVEFORM OF BUSY ARBITRATION CONTROLLED BY CE TIMING (1)

ADDR 'A'

and 'B'

ADDRESSES MATCH

CE'B'

CE'A'

BUSY'A'

tAPS(2)

tBAC

tBDC

2691 drw 12

TIMING WAVEFORM OF BUSY ARBITRATION CONTROLLED BY ADDRESS MATCH TIMING (1)

ADDR'A'

ADDR'B'

(2)

tAPS

tRC OR tWC

ADDRESSES MATCH

ADDRESSES DO NOT MATCH

tBAA

tBDA

BUSY'B'

2691 drw 13

NOTES:

1. All timing is the same for left and right ports. Port 'A' may be either left or right port. Port 'B' is the opposite from port 'A'.

2. If tAPS is not satisified, the BUSY will be asserted on one side or the other, but there is no guarantee on which side BUSY will be

asserted (71321 only).

6.03

9