AD7701 查看數據表(PDF) - Analog Devices

零件编号

产品描述 (功能)

比赛名单

AD7701 Datasheet PDF : 20 Pages

| |||

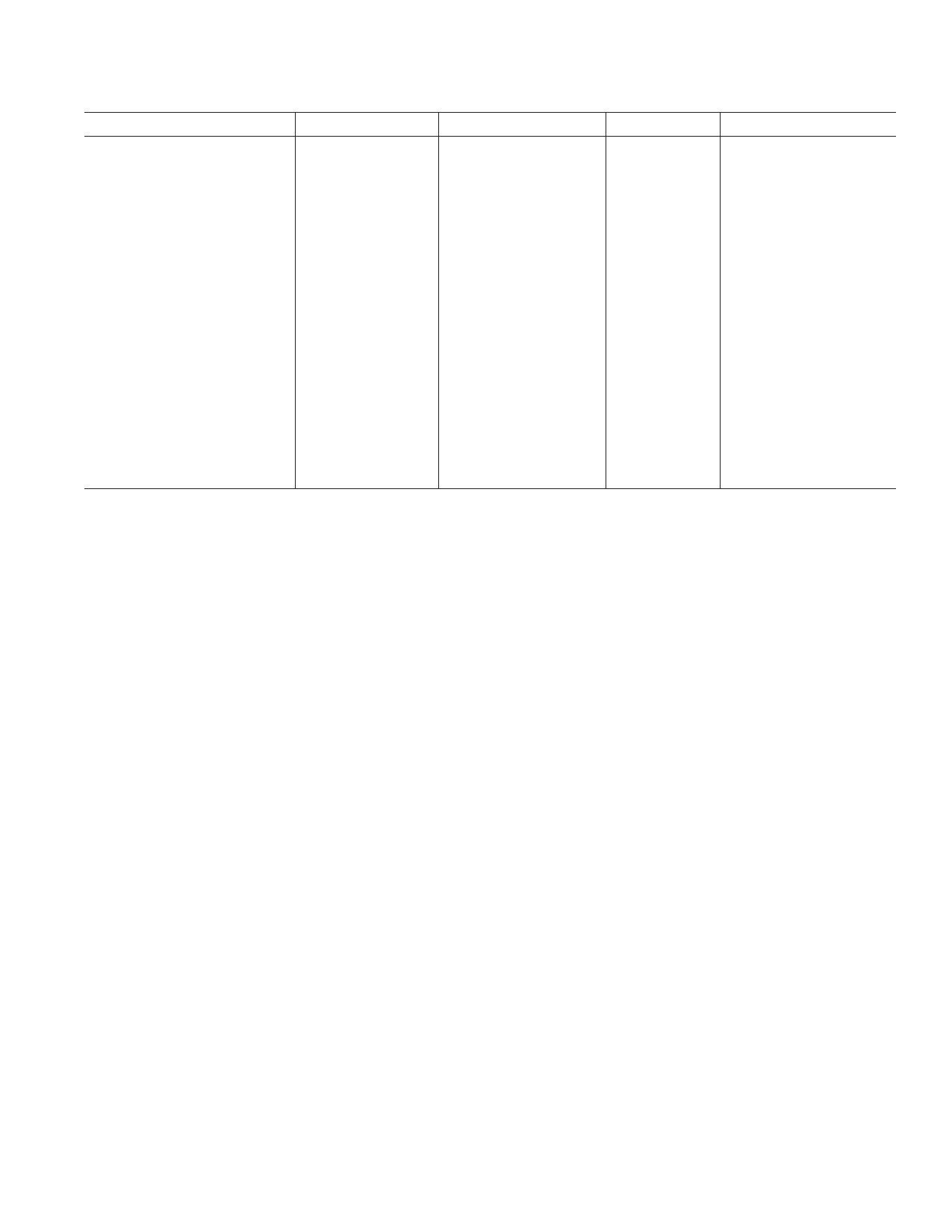

AD7701

Parameter

A, S Version2

B, T Version2

Unit

Test Conditions/Comments

POWER REQUIREMENTS8

Power Supply Voltages

Analog Positive Supply (AVDD)

Digital Positive Supply (DVDD)

Analog Negative Supply (AVSS)

Digital Negative Supply (DVSS)

Calibration Memory Retention

Power Supply Voltage

DC Power Supply Currents8

Analog Positive Supply (AIDD)

Digital Positive Supply (DIDD)

Analog Negative Supply (AISS)

Digital Negative Supply (DISS)

Power Supply Rejection9

Positive Supplies

Negative Supplies

Power Dissipation

Normal Operation

Standby Operation10

4.5/5.5

4.5/AVDD

–4.5/–5.5

–4.5/–5.5

2.0

2.7

2

2.7

0.1

70

75

37

20 (40 S Version)

4.5/5.5

4.5/AVDD

–4.5/–5.5

–4.5/–5.5

2.0

2.7

2

2.7

0.1

70

75

37

20 (40 T Version)

V min/V max

V min/V max

V min/V max

V min/V max

V min

mA max

mA max

mA max

mA max

dB typ

dB typ

mW max

µW max

Typically 2 mA

Typically 1 mA

Typically 2 mA

Typically 0.03 mA

SLEEP = Logic 1,

Typically 25 mW

SLEEP = Logic 0,

Typically 10 µW

NOTES

1The AIN pin presents a very high impedance dynamic load that varies with clock frequency.

2Temperature ranges are as follows: A, B Versions: –40°C to +85°C; S, T Versions: –55°C to +125°C.

3Apply after calibration at the temperature of interest. Full-scale error applies for both unipolar and bipolar input ranges.

4Total drift over the specified temperature range since calibration at power-up at 25 °C. This is guaranteed by design and/or characterization. Recalibration at

any temperature will remove these errors.

5In Unipolar mode, the offset can have a negative value (–V REF) such that the Unipolar mode can mimic Bipolar mode operation.

6The specifications for input overrange and for input span apply additional constraints on the offset calibration range.

7For Unipolar mode, input span is the difference between full scale and zero scale. For Bipolar mode, input span is the difference between positive and

negative full-scale points. When using less than the maximum input span, the span range may be placed anywhere within the range of ± (VREF +0.1).

8All digital outputs unloaded. All digital inputs at 5 V CMOS levels.

9Applies in 0.1 Hz to 10 Hz bandwidth. PSRR at 60 Hz will exceed 120 dB due to the digital filter.

10CLKIN is stopped. All digital inputs are grounded.

Specifications subject to change without notice.

REV. E

–3–