CMX631A 查看數據表(PDF) - CML Microcircuits

零件编号

产品描述 (功能)

比赛名单

CMX631A Datasheet PDF : 16 Pages

| |||

Low Voltage SPM Detector

CMX631A

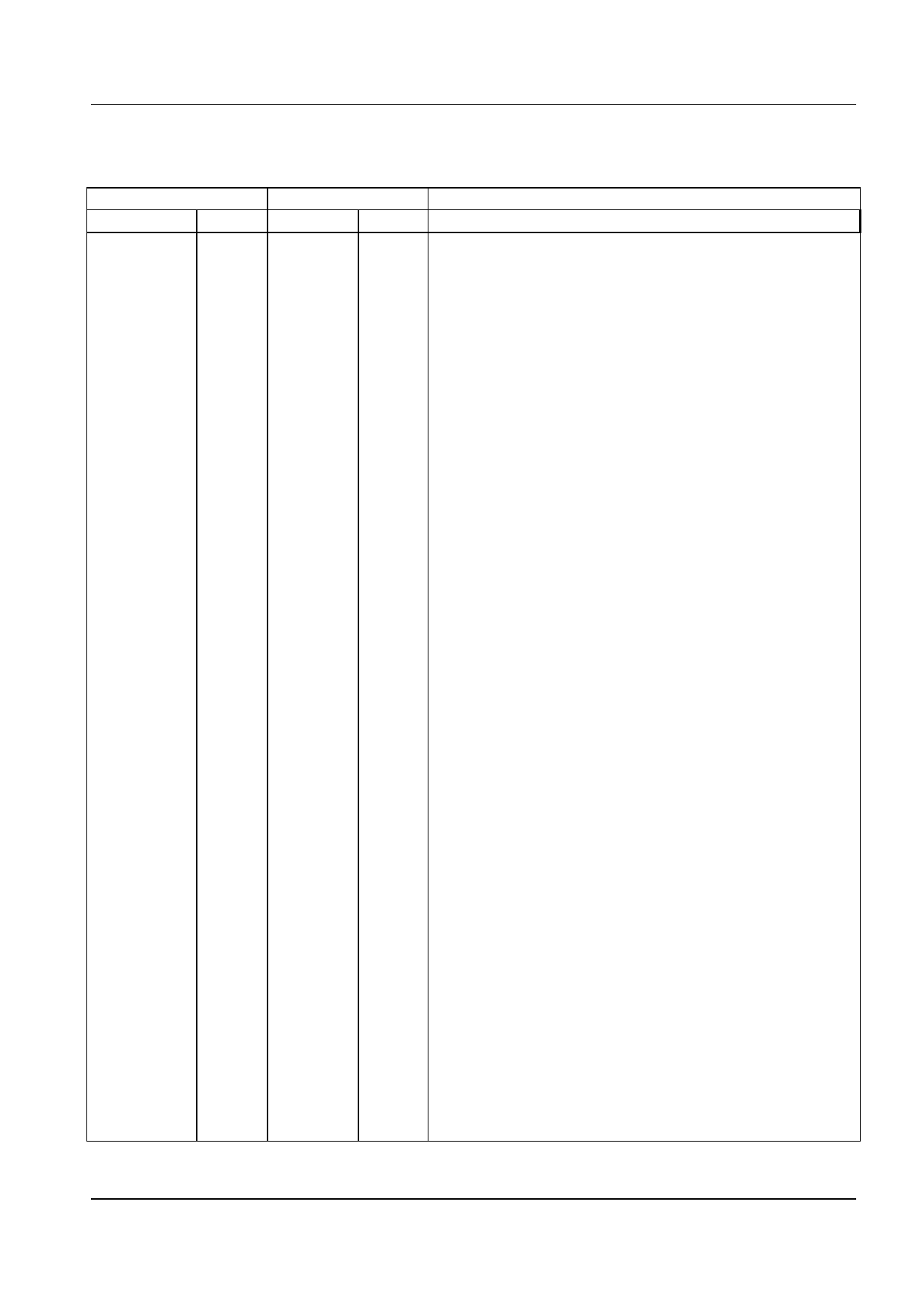

2 Signal List

Packages

D5

1

4

5

6

8

12

13

17

18

19

20

21

24

2, 3, 7, 9, 10,

11, 14, 15,

16, 22, 23

D4/P3

1

Signal

Name

Xtal/Clock

Type

I/P

2 XtalN

O/P

3 Clock Out O/P

4 Clock In I/P

7

VBIAS

Power

8

VSS

Power

9 Signal In + I/P

10 Signal In - I/P

11 Amp Out O/P

13 Tone

O/P

Follower

Output

14 Packet

O/P

Mode

Output

15 System I/P

16

VDD

Power

5,6,12 N/C

Description

The input to the on-chip clock oscillator; for use with a

3.579545MHz Xtal in conjunction with the Xtal output; circuit

components are on-chip. When using a Xtal input, the Clock

Out pin should be connected directly to the Clock In pin. If a

clock pulse input is used at the Clock In pin, this (Xtal/Clock)

pin must be connected directly to VDD . See Figure 2 and

Section 3 - External Components.

The output of the on-chip clock oscillator inverter.

A clock signal derived from the on-chip Xtal oscillator. If the

on-chip oscillator is used, this pin should be connected

directly to the Clock In pin. This output should not be used to

clock other devices

The 3.579545MHz clock pulse input to the internal clock

dividers. If an externally generated clock pulse is used, the

Xtal/Clock input pin should be connected to VDD. See

Section 3 External Components.

The output of the on-chip bias circuitry. Held internally at

VDD/2, this pin should be de-coupled to VSS. See Figure 2.

Negative supply (GND).

The positive input to the input gain adjusting signal amplifier.

See Section 4.3, Sensitivity Setting and 4.4, ‘Will’/’Will Not’

Detect Frequencies.

The negative input to the input gain adjusting signal

amplifier. See Section 4.3, Sensitivity Setting and 4.4,

‘Will’/’Will Not’ Detect Frequencies.

The output of the input gain adjusting signal amplifier. See

Section 4.3, Sensitivity Setting and 4.4, ‘Will’/’Will Not’

Detect Frequencies.

This output provides a logic ‘0’ for the period of a detected

tone and a logic ‘1’ for a NOTONE detection. See 4.1, Tone

Follower Mode and Figure 3.

This output provides a logic ‘0’ for a detected tone and a

logic 1 for NOTONE detection and will ignore a small

fluctuation or fade during the tone signal. See Section 4.2,

Packet Mode and Figure 3.

This logic input selects the device operation to either 12kHz

(logic 1) or 16kHz (logic ‘0’) SPM systems. This input has an

internal 1MΩ pull-up resistor (12kHz).

Positive supply. A single, stable power supply is required.

Critical levels and voltages within the CMX631A are

dependent upon this supply. This pin should be de-coupled

to VSS by a capacitor mounted close to the pin. Note: If this

device is line powered, the resulting power supply must be

stable. See Section 5.1.1 - Protection against High Voltages.

No internal connection; leave open circuit.

© 1998 Consumer Microcircuits Limited

4

D/631A/1