IDT7024 查看數據表(PDF) - Integrated Device Technology

零件编号

产品描述 (功能)

比赛名单

IDT7024 Datasheet PDF : 22 Pages

| |||

IDT7024S/L

High-Speed 4K x 16 Dual-Port Static RAM

read a zero into Semaphore 1. If the right processor performs a similar task

with Semaphore 0, this protocol would allow the two processors to swap

2K blocks of Dual-Port RAM with each other.

The blocks do not have to be any particular size and can even be

variable, depending upon the complexity of the software using the

semaphore flags. All eight semaphores could be used to divide the Dual-

Port RAM or other shared resources into eight parts. Semaphores can

even be assigned different meanings on different sides rather than being

given a common meaning as was shown in the example above.

Semaphores are a useful form of arbitration in systems like disk

interfaces where the CPU must be locked out of a section of memory during

a transfer and the I/O device cannot tolerate any wait states. With the use

of semaphores, once the two devices has determined which memory area

was “off-limits” to the CPU, both the CPU and the I/O devices could access

their assigned portions of memory continuously without any wait states.

Military, Industrial and Commercial Temperature Ranges

Semaphores are also useful in applications where no memory “WAIT”

state is available on one or both sides. Once a semaphore handshake has

been performed, both processors can access their assigned RAM

segments at full speed.

Another application is in the area of complex data structures. In this

case, block arbitration is very important. For this application one processor

may be responsible for building and updating a data structure. The other

processor then reads and interprets that data structure. If the interpreting

processor reads an incomplete data structure, a major error condition may

exist. Therefore, some sort of arbitration must be used between the two

different processors. The building processor arbitrates for the block, locks

it and then is able to go in and update the data structure. When the update

is completed, the data structure block is released. This allows the

interpreting processor to come back and read the complete data structure,

thereby guaranteeing a consistent data structure.

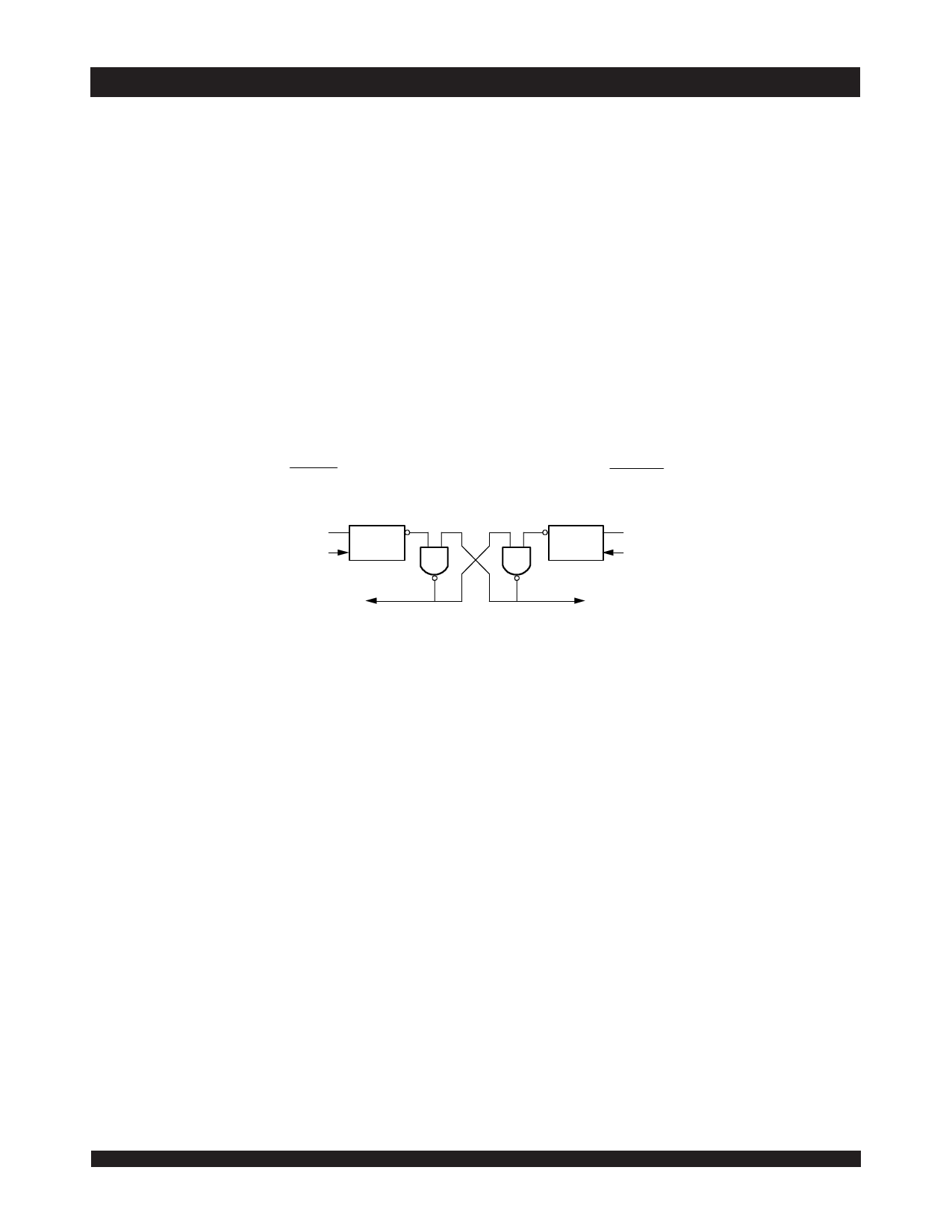

L PORT

SEMAPHORE

REQUEST FLIP FLOP

D0

D

Q

WRITE

R PORT

SEMAPHORE

REQUEST FLIP FLOP

Q

D

D0

WRITE

SEMAPHORE

READ

SEMAPHORE

READ

,

2740 drw 20

Figure 4. IDT7024 Semaphore Logic

62.402