LIS3L02DQ 查看數據表(PDF) - STMicroelectronics

零件编号

产品描述 (功能)

比赛名单

LIS3L02DQ Datasheet PDF : 19 Pages

| |||

LIS3L02DQ

4.1 I2C Serial Interface

The LIS3L02DQ I2C is a bus slave. The I2C is employed to write the data into the registers whose content

can also be read back.

The relevant I2C terminology is given in the table below

Table 6. Serial Interface Pin Description

Term

Description

Transmitter

The device which sends data to the bus

Receiver

The device which receives data from the bus

Master

The device which initiates a transfer, generates clock signals and terminates a transfer

Slave

The device addressed by the master

There are two signals associated with the I2C bus: the Serial Clock Line (SCL) and the Serial DAta line

(SDA). The latter is a bidirectional line used for sending and receiving the data to/from the interface. Both

the lines are connected to Vdd through a pull-up resistor embedded inside the LIS3L02DQ. When the bus

is free both the lines are high.

4.1.1 I2C Operation

The transaction on the bus is started through a START signal. A START condition is defined as a HIGH

to LOW transition on the data line while the SCL line is held HIGH. After this has been transmitted by the

Master, the bus is considered busy. The next byte of data transmitted after the start condition contains the

address of the slave in the first 7 bits and the eighth bit tells whether the Master is receiving data from the

slave or transmitting data to the slave. When an address is sent, each device in the system compares the

first seven bits after a start condition with its address. If they match, the device considers itself addressed

by the Master. The address can be made up of a programmable part and a fixed part, thus allowing more

than one device of the same type to be connected to the I2C bus.

The Slave ADdress (SAD) associated to the LIS3L02DQ is 0011101.

Data transfer with acknowledge is mandatory. The transmitter must release the SDA line during the ac-

knowledge pulse. The receiver must then pull the data line LOW so that it remains stable low during the

HIGH period of the acknowledge clock pulse. A receiver which has been addressed is obliged to generate

an acknowledge after each byte of data has been received.

The I2C embedded inside the LIS3L02DQ behaves like a slave device and the following protocol must be

adhered to. After the start condition (ST) a salve address is sent, once a slave acknowledge has been

returned, a 8-bit sub-address will be transmitted: the 7 LSB represent the actual register address while the

MSB enables address autoincrement. If the MSB of the SUB field is 1, the SUB (register address) will be

automatically incremented to allow multiple data read/write.

If the LSB of the slave address was ‘1’ (read), a repeated START condition will have to be issued after the

two sub-address bytes; if the LSB is ‘0’ (write) the Master will transmit to the slave with direction un-

changed.

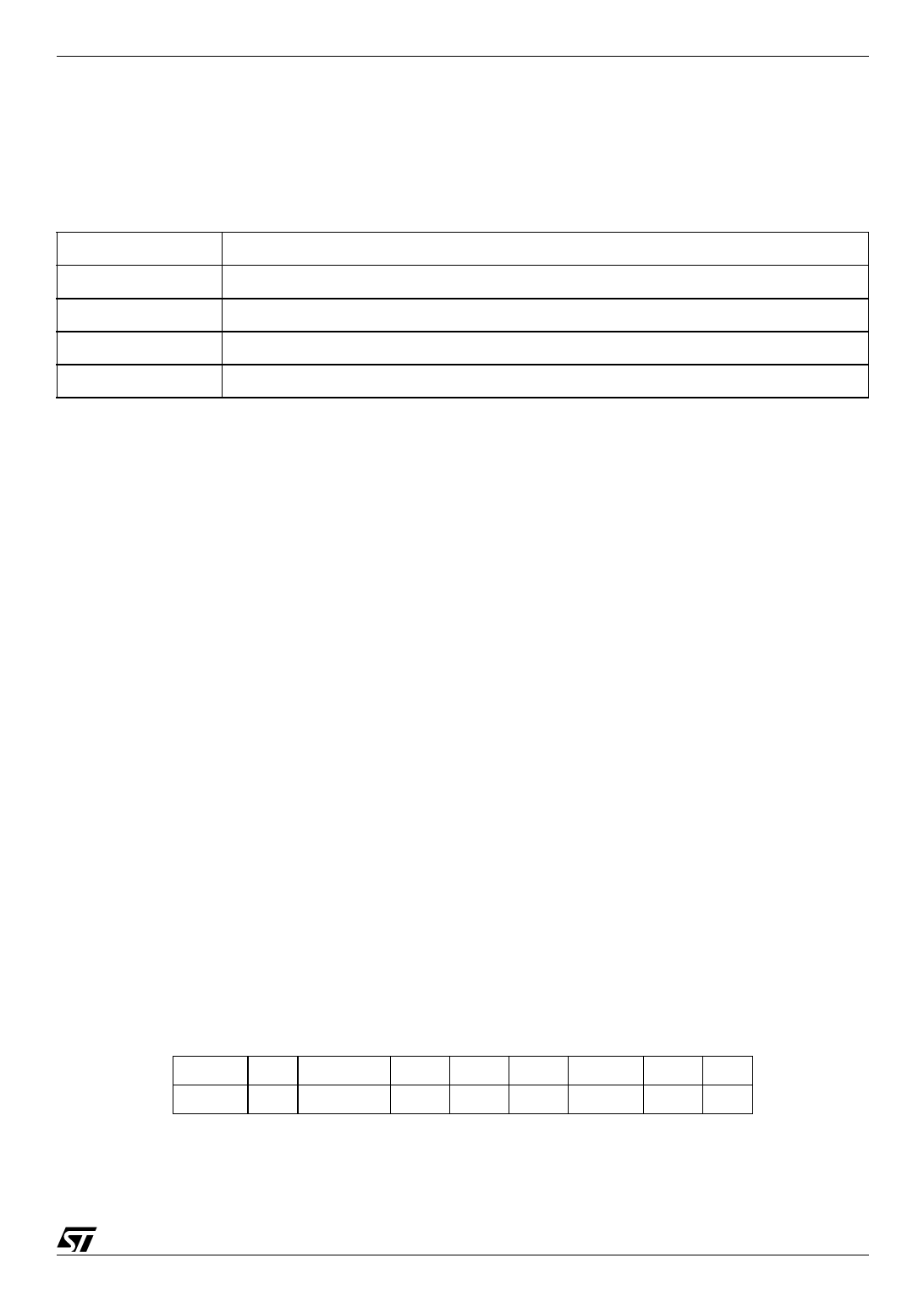

Transfer when Master is writing one byte to slave

Master ST SAD + W

SUB

Slave

SAK

SAK

DATA

SP

SAK

7/19