NJU3504FA1 查看數據表(PDF) - Japan Radio Corporation

零件编号

产品描述 (功能)

比赛名单

NJU3504FA1 Datasheet PDF : 60 Pages

| |||

NJU3504

• STACK POINTER(SP)

STACK POINTER(SP) consists of the 3 bits binary counter. SP indicates the number of next operating

position in the STACK. It counts one up(increment) after the subroutine call(CALL) or the interrupt

operation, and it counts one down(decrement) after the return(RET or RETI) operation.

Data storing operation to STACK after that SP overflowed(over than 7) or under flowed(under than 0),

breaks the former held data in STACK. Therefore the subroutine nesting level must be cautioned in the

application program.

SP condition is set to "0" on “RESET” operation.

• DATA MEMORY(RAM)

DATA MEMORY(RAM) is formed with the 4-bit length a word. The NJU3504 prepares 256 words(1024

bits) RAM. The data formed with the 4-bit length a word can be read/written from/to RAM, and the data

formed with the 1-bit length in a word can be set, reset, or tested by the bit-operation instruction.

The RAM address is indicated indirectly by X- and Y-reg.

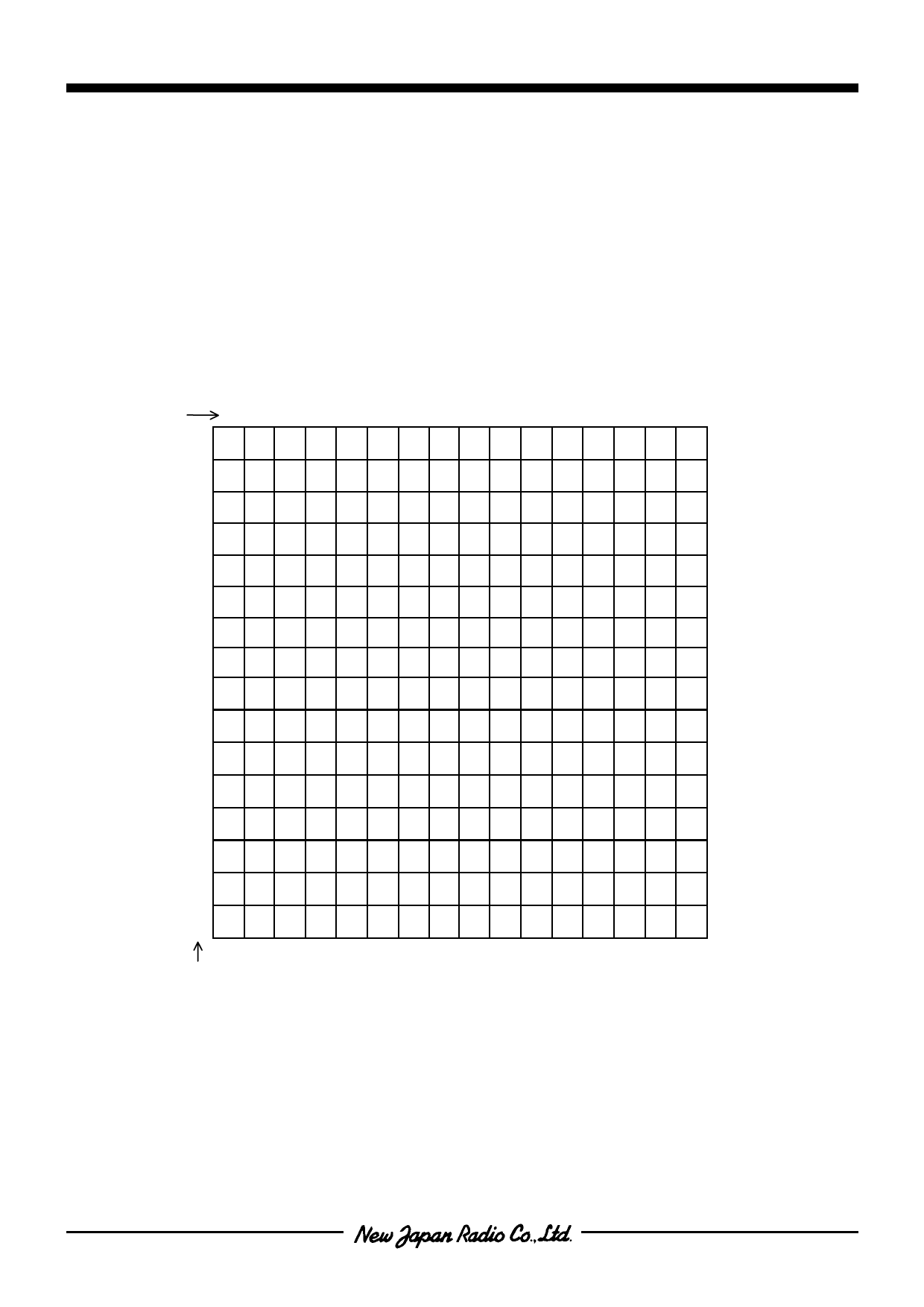

[RAM ADDRESS MAP]

Y-reg

0 1 2 3 4 5 6 7 8 9 A B C D E F [HEX]

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

[HEX]

X-reg

- 10 -