UPC1935 查看數據表(PDF) - NEC => Renesas Technology

零件编号

产品描述 (功能)

比赛名单

UPC1935 Datasheet PDF : 28 Pages

| |||

µ PC1935

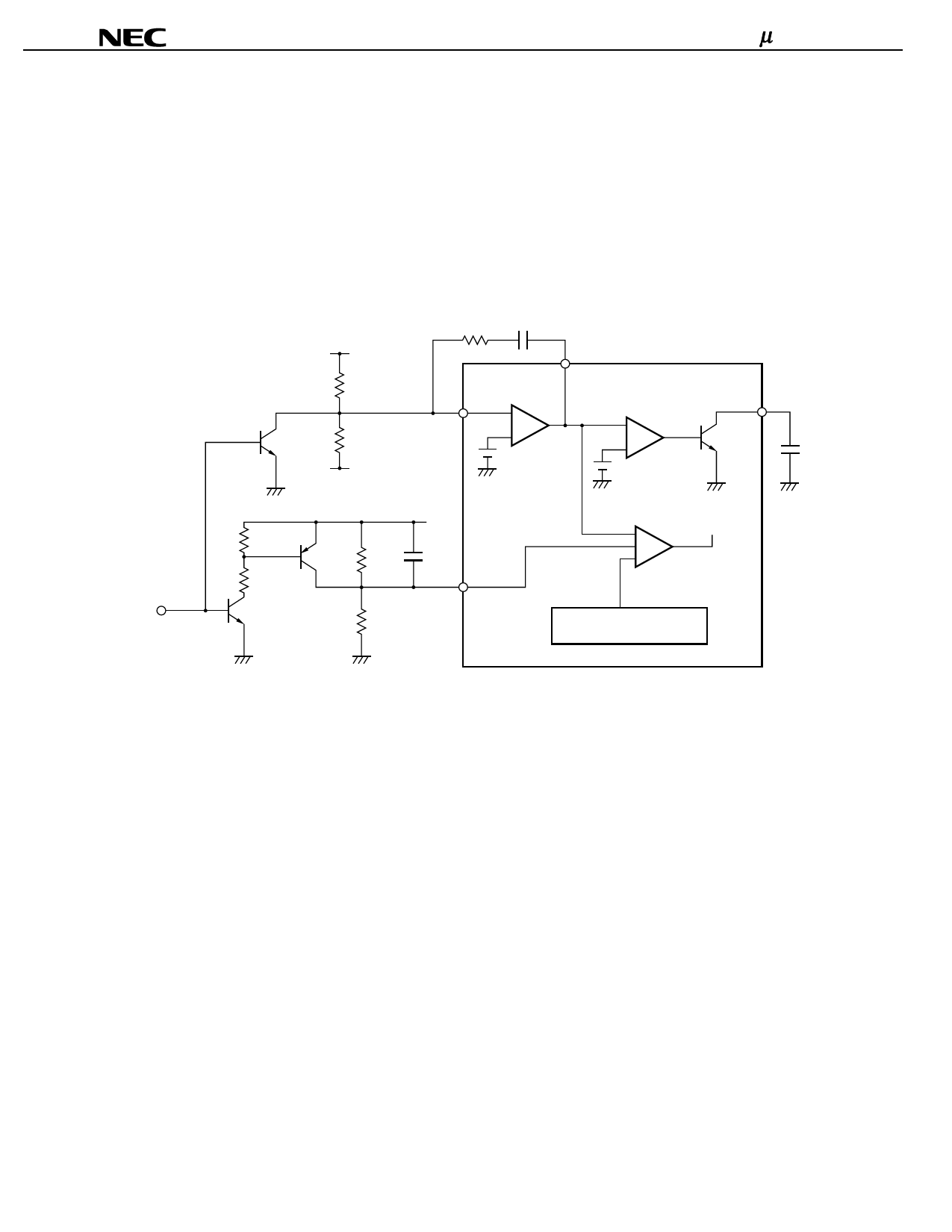

3.5.3 Channel 3 (for inverted output)

The ON/OFF signal control method of the output oscillation of channel 3 is to input the ON/OFF signal from ON3 as

shown in Figure 3-5. The PWM converter can be turned ON/OFF by controlling the level of the DTC3 pin. However, it is

necessary to keep the level of the FB3 output high so that the timer latch does not start when the PWM converter is OFF.

In this circuit example, the FB3 output level is controlled by controlling the level of the II3 pin.

Because channel 3 supports an inverted converter, its PWM comparator logic is different from that of channels 1 and 2.

Figure 3-5 ON/OFF Control (channel 3: for inverted output)

ON3

Q33

Q31

VREF

R31

R32

–VO3

(Converter

output voltage)

FB3

II3

–

SCP comparator

(common to each channel) DLY

+

+ Error

Q1

0.3 V amplifier

–

0.63 V

Q32

VREF

R33

C31

To output stage

–

–

+

PWM comparator

DTC3

R34

Oscillation section

(common to each channel)

CDLY

(1) When ON3 is high: OFF status

Q31: ON → Q32: ON → DTC3 pin: High level → Output duty of PWM comparator: 0 %

Q33: ON → II3 pin: Low level → FB3 output: High level → SCP comparator output: High level → Q1 is ON.

→ Timer latch stops.

(2) When ON3 is low: ON status

Q31: OFF → Q32 is OFF. → C31 is charged in the sequence of [VREF → C31 → R34] → DTC3 pin voltage drops.

→ Soft start

Q33: OFF → II3 pin: High level → FB3 output: Low level → SCP comparator output: Low level → Q1: OFF

→ Charging CDLY starts (timer latch start).

Caution Keep the high-level voltage of the DTC3 pin at 1.6 V or higher and the low-level voltage of the II3 pin

within 0.3 V. The maximum voltage that is applied to the II3 pin must be equal to or lower than VREF.

Data Sheet G13418EJ3V0DS00

19