L3GD20 查看數據表(PDF) - STMicroelectronics

零件编号

产品描述 (功能)

比赛名单

L3GD20 Datasheet PDF : 44 Pages

| |||

L3GD20

Digital main blocks

4.2.1

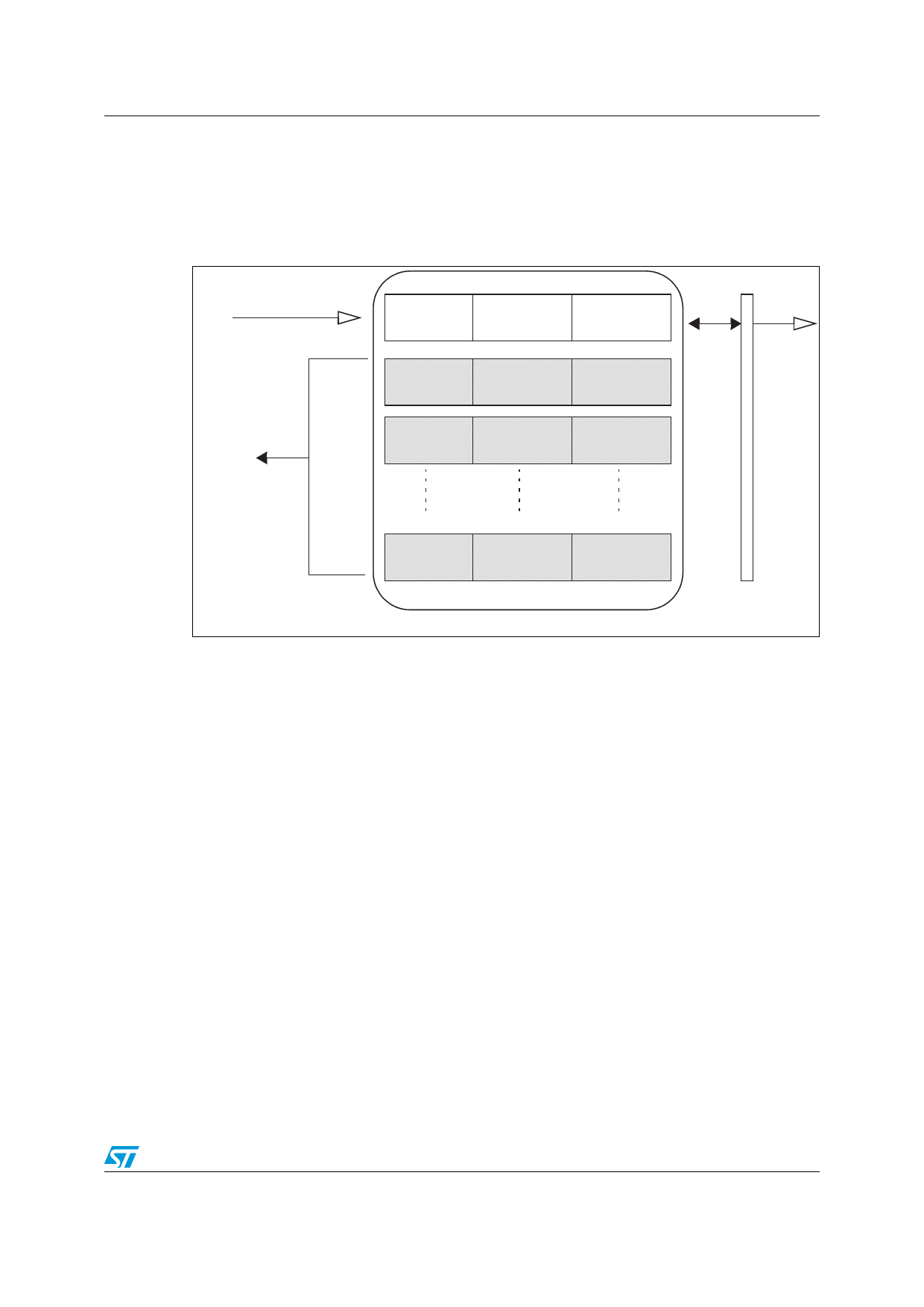

Bypass mode

In Bypass mode, the FIFO is not operational and for this reason it remains empty. As

described in Figure 7 below, for each channel only the first address is used. The remaining

FIFO slots are empty. When new data is available, the old data is overwritten.

Figure 7. Bypass mode

xi,yi,zi

x0

yi0

z0

empty

x1

y1

z1

x2

y2

z2

x31

y31

z31

4.2.2

AM07231v1

FIFO mode

In FIFO mode, data from the yaw, pitch and roll channels is stored in the FIFO. A watermark

interrupt can be enabled (I2_WMK bit into CTRL_REG3 (22h)) in order to be raised when

the FIFO is filled to the level specified in the WTM 4:0 bits of FIFO_CTRL_REG (2Eh). The

FIFO continues filling until it is full (32 slots of 16-bit data for yaw, pitch and roll). When full,

the FIFO stops collecting data from the input channels. To restart data collection, the

FIFO_CTRL_REG (2Eh) must be written back to Bypass mode.

FIFO mode is represented in Figure 8: FIFO mode.

Doc ID 022116 Rev 1

17/44