HS-80C86RH 查看數據表(PDF) - Intersil

零件编号

产品描述 (功能)

比赛名单

HS-80C86RH Datasheet PDF : 29 Pages

| |||

HS-80C86RH

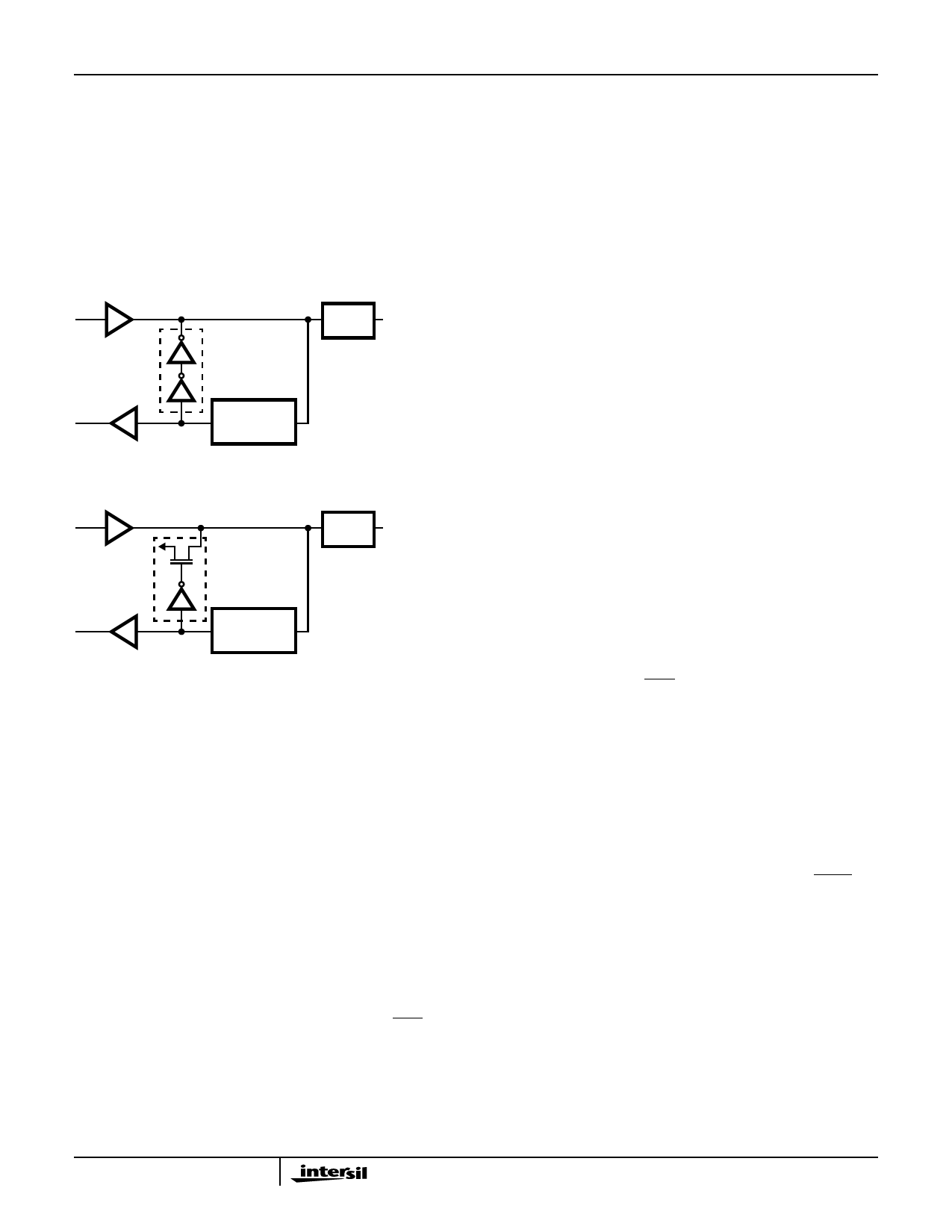

and 12B). These circuits will maintain the last valid logic

state if no driving source is present (i.e., an unconnected pin

or a driving source which goes to a high impedance state).

To overdrive the “bus hold” circuits, an external driver must

be capable of supplying approximately 400µA minimum sink

or source current at valid input voltage levels. Since this “bus

hold” circuitry is active and not a “resistive” type element, the

associated power supply current is negligible and power

dissipation is significantly reduced when compared to the

use of passive pull-up resistors.

OUTPUT

DRIVER

BOND

PAD

EXTERNAL

PIN

INPUT

BUFFER

INPUT

PROTECTION

CIRCUITRY

FIGURE 12A. BUS HOLD CIRCUITRY PIN 2-16, 34-39

VCC P

OUTPUT

DRIVER

INPUT

BUFFER

INPUT

PROTECTION

CIRCUITRY

BOND

PAD

EXTERNAL

PIN

FIGURE 12B. BUS HOLD CIRCUITRY PIN 26-32

Interrupt Operations

Interrupt operations fall into two classes: software or

hardware initiated. The software initiated interrupts and

software aspects of hardware interrupts are specified in the

Instruction Set Description. Hardware interrupts can be

classified as non-maskable or maskable.

Interrupts result in a transfer of control to a new program

location. A 256-element table containing address pointers to

the interrupt service routine locations resides in absolute

locations 0 through 3FFH, which are reserved for this

purpose. Each element in the table is 4 bytes in size and

corresponds to an interrupt “type”. An interrupting device

supplies an 8-bit type number during the interrupt

acknowledge sequence, which is used to “vector” through

the appropriate element to the interrupt service routine

location. All flags and both the Code Segment and

Instruction Pointer register are saved as part of the INTA

sequence. These are restored upon execution of an Interrupt

Return (lRET) instruction.

Non-Maskable Interrupt (NMI)

The processor provides a single non-maskable interrupt pin

(NMl) which has higher priority than the maskable interrupt

request pin (INTR). A typical use would be to activate a

power failure routine. The NMl is edge-triggered on a LOW-

to-HIGH transition. The activation of this pin causes a type 2

interrupt.

NMl is required to have a duration in the HIGH state of

greater than 2 CLK cycles, but is not required to be

synchronized to the clock. Any positive transition of NMl is

latched on-chip and will be serviced at the end of the current

instruction or between whole moves of a block-type

instruction. Worst case response to NMl would be for

multiply, divide, and variable shift instructions. There is no

specification on the occurrence of the low-going edge; it may

occur before, during or after the servicing of NMl. Another

positive edge triggers another response if it occurs after the

start of the NMl procedure. The signal must be free of logical

spikes in general and be free of bounces on the low-going

edge to avoid triggering extraneous responses.

Maskable Interrupt (INTR)

The HS-80C86RH provides a single interrupt request input

(INTR) which can be masked internally by software with the

resetting of the interrupt enable flag (IF) status bit. The

interrupt request signal is level triggered. It is internally

synchronized during each clock cycle on the high-going

edge of CLK. To be responded to, INTR must be present

(HIGH) during the clock period preceding the end of the

current instruction or the end of a whole move for a block-

type instruction. INTR may be removed anytime after the

falling edge of the first INTA signal. During the interrupt

response sequence further interrupts are disabled. The

enable bit is reset as part of the response to any interrupt

(INTR, NMl, software interrupt or single-step), although the

FLAGS register which is automatically pushed onto the stack

reflects the state of the processor prior to the interrupt. Until

the old FLAGS register is restored the enable bit will be zero

unless specifically set by an instruction.

During the response sequence (Figure 13) the processor

executes two successive (back-to-back) interrupt

acknowledge cycles. The HS-80C86RH emits the LOCK

signal (Max mode only) from T2 of the first bus cycle until T2

of the second. A local bus “hold” request will not be honored

until the end of the second bus cycle. In the second bus

cycle, a byte is supplied to the HS-80C86RH by the

HS-82C89ARH Interrupt Controller, which identifies the

source (type) of the interrupt. This byte is multiplied by four

and used as a pointer into the interrupt vector lookup table.

An INTR signal left HIGH will be continually responded to

within the limitations of the enable bit and sample period.

The INTERRUPT RETURN instruction includes a FLAGS

pop which returns the status of the original interrupt enable

bit when it restores the FLAGS.

20