CDB6403 查看數據表(PDF) - Cirrus Logic

零件编号

产品描述 (功能)

比赛名单

CDB6403 Datasheet PDF : 54 Pages

| |||

CS6403

cept for the SSI, though writes to any control bit

except RST are ignored. Power down is not en-

abled.

Upon exiting Reset, control registers and RAM

are cleared, and then control constants are loaded

into Data RAM from the Program ROM.

Power-Down

Power Down is initiated by setting the Sleep bit

in SSI Control Register 0 (SLP: SSI_CR0.10).

In Power Down, the CPU and the AFP are pow-

ered down, but the SSI and the Codec are still

operational. Power Down is only accessible in

Mode 2 (16-bit).

Since the SSI and the Codec are active during

Power Down, it is possible to serially transfer

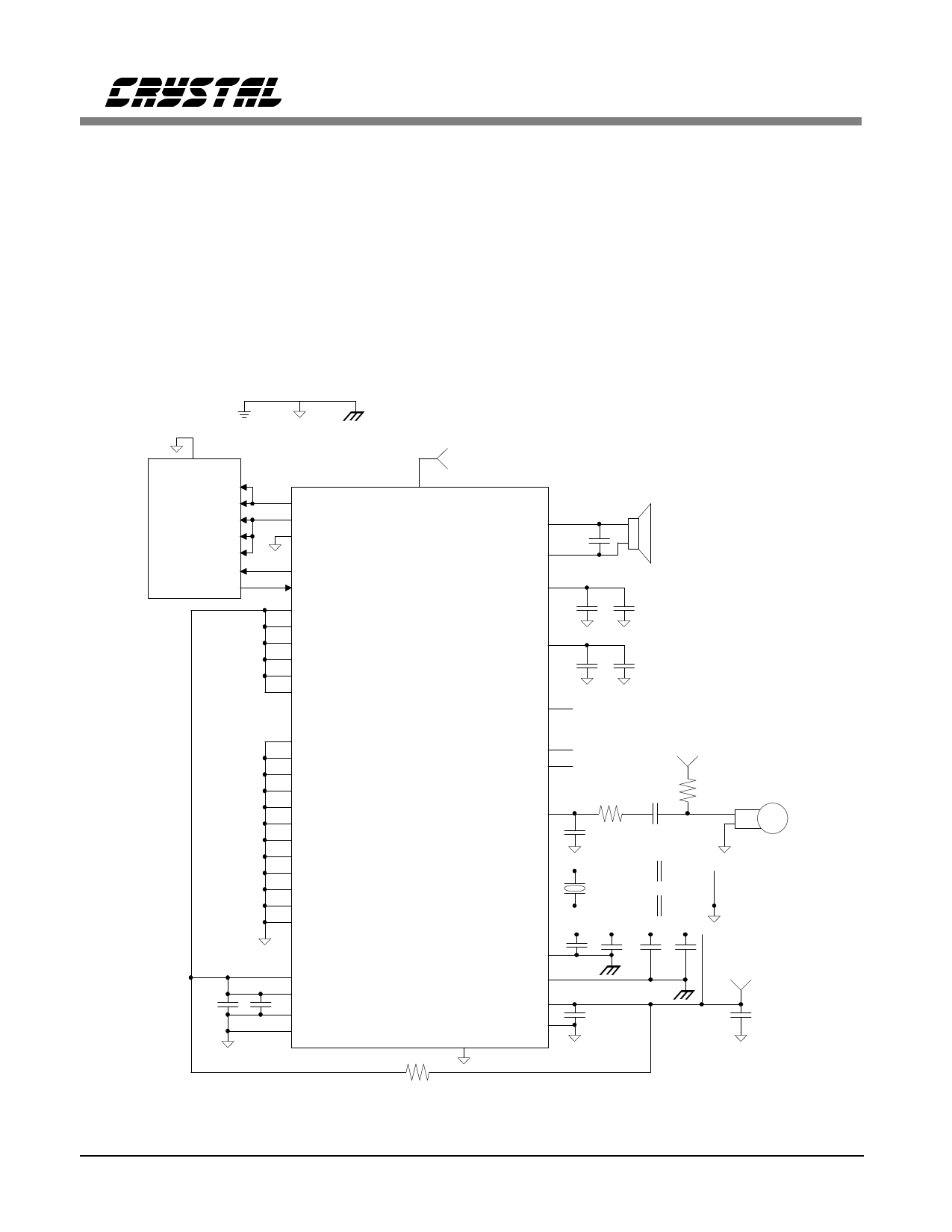

Digital Analog Speaker

Ground Ground Ground

External

µ-law FSR

Codec FST

BCLKR

BCLKT

MCLK

DR

DT

SYNCOUT

SCLK

SSYNC

SDO

SDI

RESERVED1

SCLK_RATE0

SCLK_RATE1

SMASTER

SFRAME

UALAW

CLK_SEL

CONFIG

GPIN0

GPIN1

GPIN2

GPIN3

RESERVED0

RESERVED2

RESERVED3

RESERVED4

RESERVED5

RESERVED6

+

1 µF

0.1 µF

DVDD0

DVDD1

DGND1

DGND0

System

Reset

RESET

CS6403

SPKROUTP

470 pF

8Ω

SPKROUTN

VREF

0.1µF

+ 1µF

VCM

0.1µF

+ 1µF

NC

GPOUT0

GPOUT1

Microphone

Phantom Power

Supply

MICIN

150Ω 0.47µF

2.2kΩ

CLKIN

CLKOUT

0.022µF

NPO

8.192MHz

33 pF

33 pF

Microphone

PVDD

PGND0

PGND1

0.1 µF 0.1 µF 0.1 µΦ 0.1 µΦ

+

+

+5V Analog

Supply

AGND1

AVDD

AGND0

0.1 µF

+

10 µF

2Ω

Figure 5. External Mu-law Codec Connection Diagram

DS192PP6

13