CDB6403 查看數據表(PDF) - Cirrus Logic

零件编号

产品描述 (功能)

比赛名单

CDB6403 Datasheet PDF : 54 Pages

| |||

CS6403

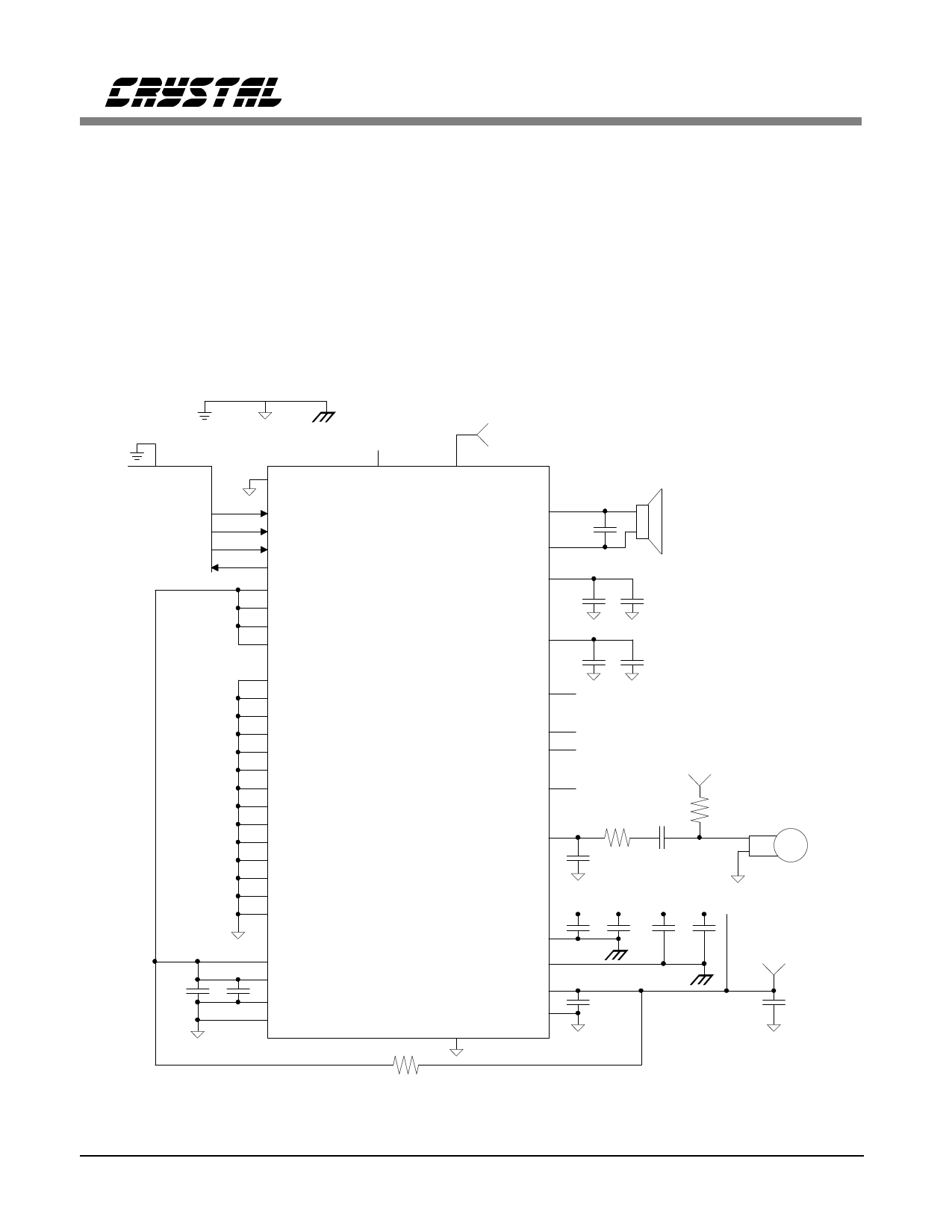

Interfacing as a Slave to an external DSP

(Mode 2)

When interfacing to an external DSP (Mode 2),

the CS6403 is configured as a slave to the DSP:

SSI; i.e., SCLK, and SSYNC signals are pro-

vided to the CS6403 by the DSP. An example of

the interface circuitry is shown in Figure 7.

In this case, the DSP sends a single start-of-

frame pulse to the SSYNC input one SCLK

period before the start of a data frame. Since

there is only one SSYNC input, every data frame

includes both a data read from the CS6403 and a

data write to the CS6403. The behavior of the

serial interface is illustrated in Figure 8.

Digital Analog Speaker

Ground Ground Ground

System

Reset

DSP

CLKIN

CLKOUT

RESET

+

1 µF

0.1 µF

SDI

SCLK

SSYNC

SDO

CONFIG

RESERVED1

SCLK_RATE0

SCLK_RATE1

CLK_SEL

GPIN0

GPIN1

GPIN2

GPIN3

RESERVED0

RESERVED2

RESERVED3

RESERVED4

RESERVED5

RESERVED6

SFRAME

SMASTER

UALAW

DVDD0

DVDD1

DGND1

DGND0

CS6403

SPKROUTP 470 pF

SPKROUTN

VREF

0.1 µF

8Ω

+ 1 µF

VCM

0.1 µF

+ 1 µF

NC

GPOUT0

GPOUT1

Microphone

Phantom Power

Supply

SYNCOUT

MICIN

150Ω 0.47µF

2.2kΩ

0.022µF

NPO

Microphone

PVDD

PGND0

PGND1

0.1 µF 0.1 µF 0.1 µF 0.1 µF

+

+

+5V Analog

Supply

AGND1

AVDD

AGND0

0.1 µF

+

10 µF

2Ω

Figure 7. DSP Connection Diagram (Mode 2)

DS192PP6

15